Register Description

R

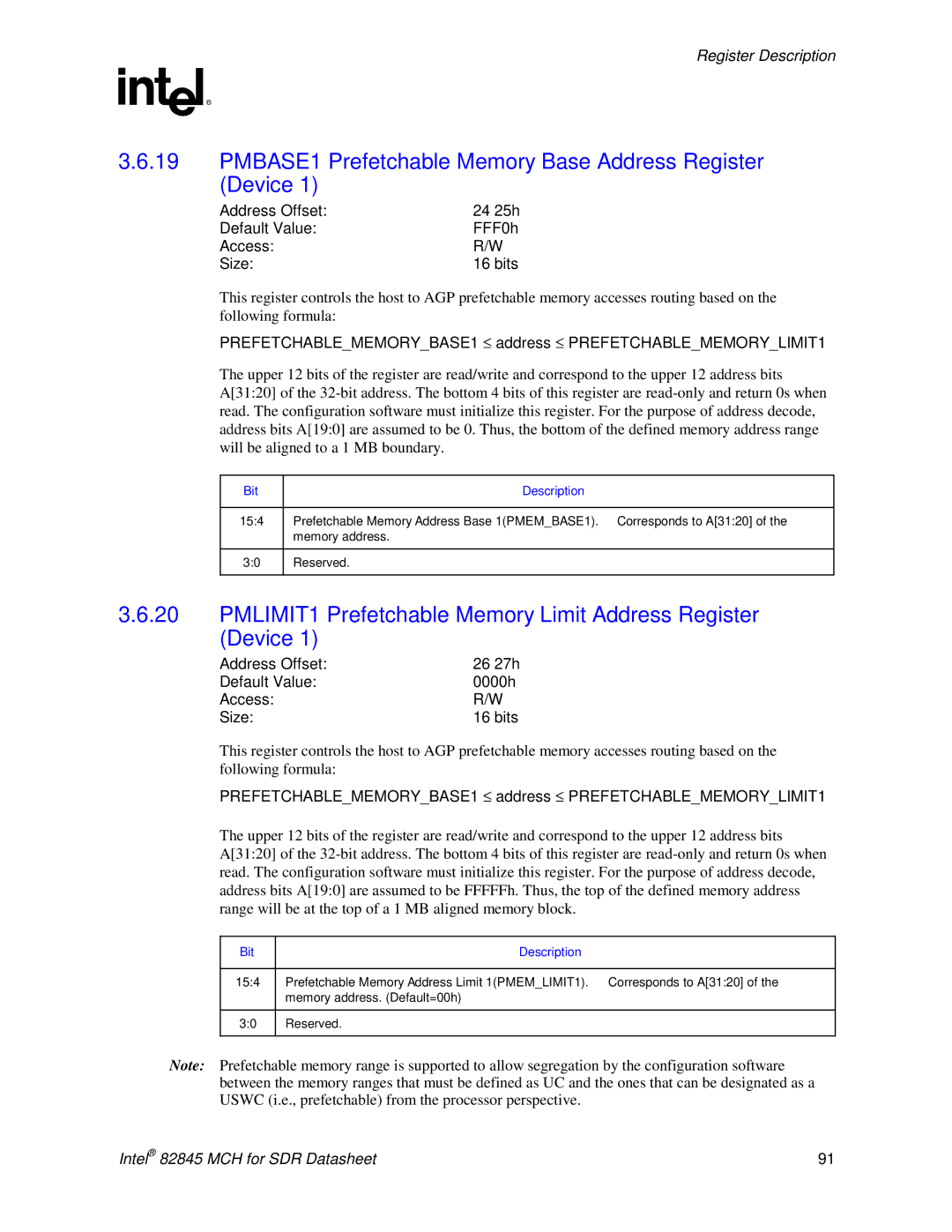

3.6.19PMBASE1—Prefetchable Memory Base Address Register (Device 1)

Address Offset: |

|

Default Value: | FFF0h |

Access: | R/W |

Size: | 16 bits |

This register controls the host to AGP prefetchable memory accesses routing based on the following formula:

PREFETCHABLE_MEMORY_BASE1 ≤ address ≤ PREFETCHABLE_MEMORY_LIMIT1

The upper 12 bits of the register are read/write and correspond to the upper 12 address bits A[31:20] of the

Bit | Description |

|

|

15:4 | Prefetchable Memory Address Base 1(PMEM_BASE1). Corresponds to A[31:20] of the |

| memory address. |

|

|

3:0 | Reserved. |

|

|

3.6.20PMLIMIT1—Prefetchable Memory Limit Address Register (Device 1)

Address Offset: |

|

Default Value: | 0000h |

Access: | R/W |

Size: | 16 bits |

This register controls the host to AGP prefetchable memory accesses routing based on the following formula:

PREFETCHABLE_MEMORY_BASE1 ≤ address ≤ PREFETCHABLE_MEMORY_LIMIT1

The upper 12 bits of the register are read/write and correspond to the upper 12 address bits A[31:20] of the

Bit | Description |

|

|

15:4 | Prefetchable Memory Address Limit 1(PMEM_LIMIT1). Corresponds to A[31:20] of the |

| memory address. (Default=00h) |

|

|

3:0 | Reserved. |

|

|

Note: Prefetchable memory range is supported to allow segregation by the configuration software between the memory ranges that must be defined as UC and the ones that can be designated as a USWC (i.e., prefetchable) from the processor perspective.

Intel® 82845 MCH for SDR Datasheet | 91 |