Register Description

R

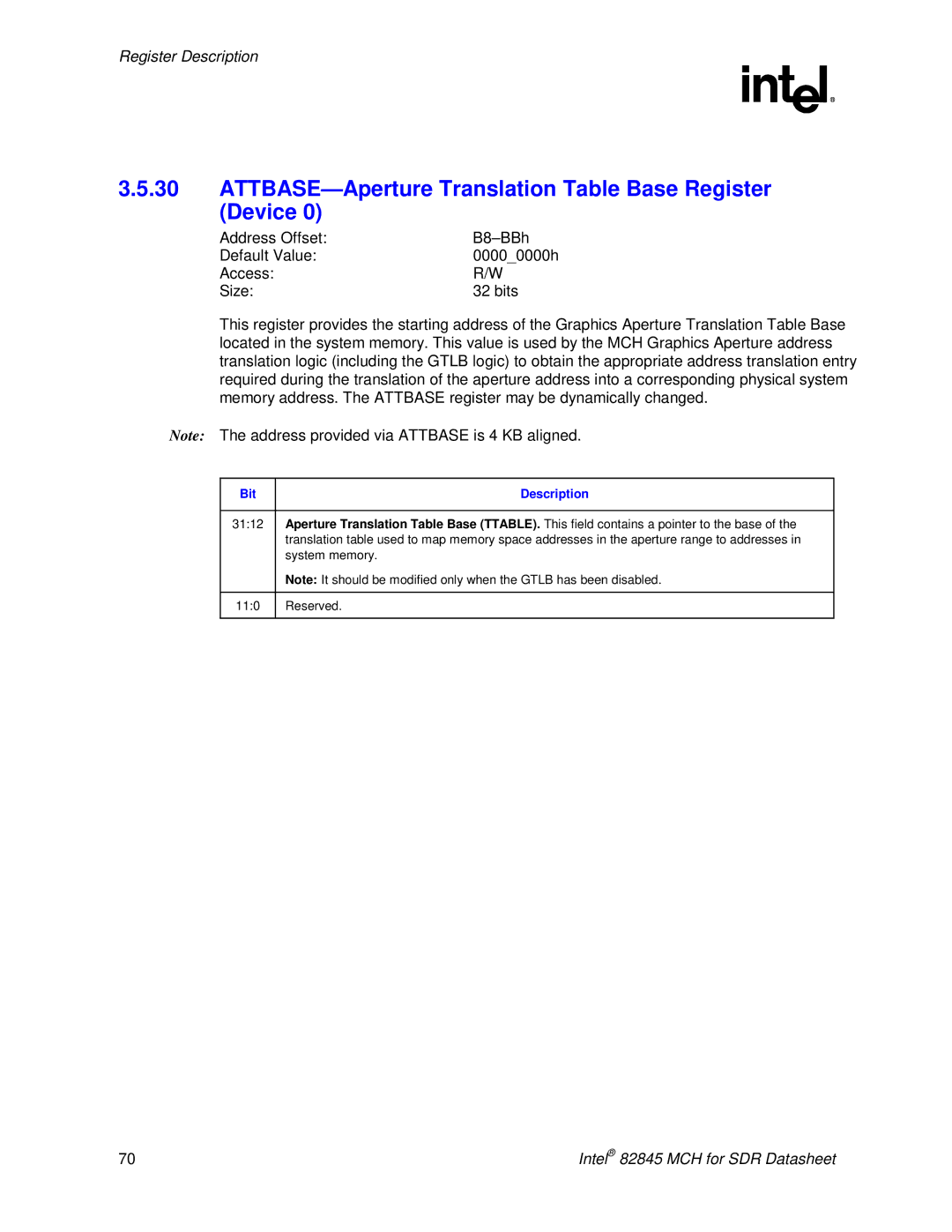

3.5.30ATTBASE—Aperture Translation Table Base Register (Device 0)

Address Offset: | |

Default Value: | 0000_0000h |

Access: | R/W |

Size: | 32 bits |

This register provides the starting address of the Graphics Aperture Translation Table Base located in the system memory. This value is used by the MCH Graphics Aperture address translation logic (including the GTLB logic) to obtain the appropriate address translation entry required during the translation of the aperture address into a corresponding physical system memory address. The ATTBASE register may be dynamically changed.

Note: The address provided via ATTBASE is 4 KB aligned.

Bit | Description |

|

|

31:12 | Aperture Translation Table Base (TTABLE). This field contains a pointer to the base of the |

| translation table used to map memory space addresses in the aperture range to addresses in |

| system memory. |

| Note: It should be modified only when the GTLB has been disabled. |

|

|

11:0 | Reserved. |

|

|

70 | Intel® 82845 MCH for SDR Datasheet |