Register Description

R

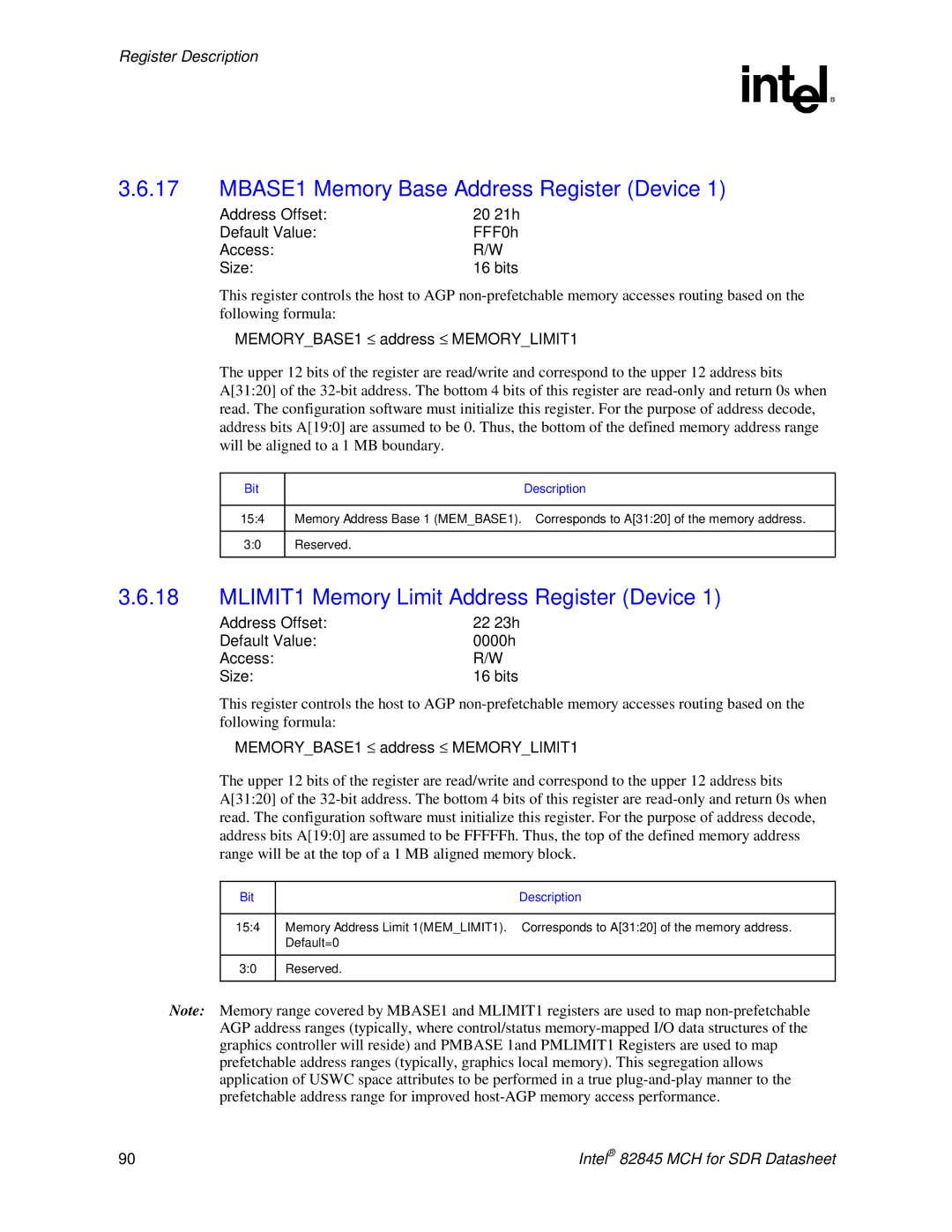

3.6.17MBASE1—Memory Base Address Register (Device 1)

Address Offset: |

|

Default Value: | FFF0h |

Access: | R/W |

Size: | 16 bits |

This register controls the host to AGP

MEMORY_BASE1 ≤ address ≤ MEMORY_LIMIT1

The upper 12 bits of the register are read/write and correspond to the upper 12 address bits A[31:20] of the

Bit | Description |

|

|

15:4 | Memory Address Base 1 (MEM_BASE1). Corresponds to A[31:20] of the memory address. |

|

|

3:0 | Reserved. |

|

|

3.6.18MLIMIT1—Memory Limit Address Register (Device 1)

Address Offset: |

|

Default Value: | 0000h |

Access: | R/W |

Size: | 16 bits |

This register controls the host to AGP

MEMORY_BASE1 ≤ address ≤ MEMORY_LIMIT1

The upper 12 bits of the register are read/write and correspond to the upper 12 address bits A[31:20] of the

Bit | Description |

|

|

15:4 | Memory Address Limit 1(MEM_LIMIT1). Corresponds to A[31:20] of the memory address. |

| Default=0 |

|

|

3:0 | Reserved. |

|

|

Note: Memory range covered by MBASE1 and MLIMIT1 registers are used to map

90 | Intel® 82845 MCH for SDR Datasheet |