Register Description

R

Bit |

| Descriptions |

|

| |

0 | Parity Error Response Enable | |

| errors on AGP. | |

| 0 | =Address and data parity errors on AGP are not reported via the MCH hub interface SERR# |

|

| messaging mechanism. Other types of error conditions can still be signaled via SERR# |

|

| messaging independent of this bit’s state. |

| 1 | =The G_PERR# signal is not implemented by the MCH. However, when this bit is set to 1, |

|

| address and data parity errors detected on AGP are reported via hub interface SERR# |

|

| messaging mechanism, if further enabled by SERRE1. |

|

|

|

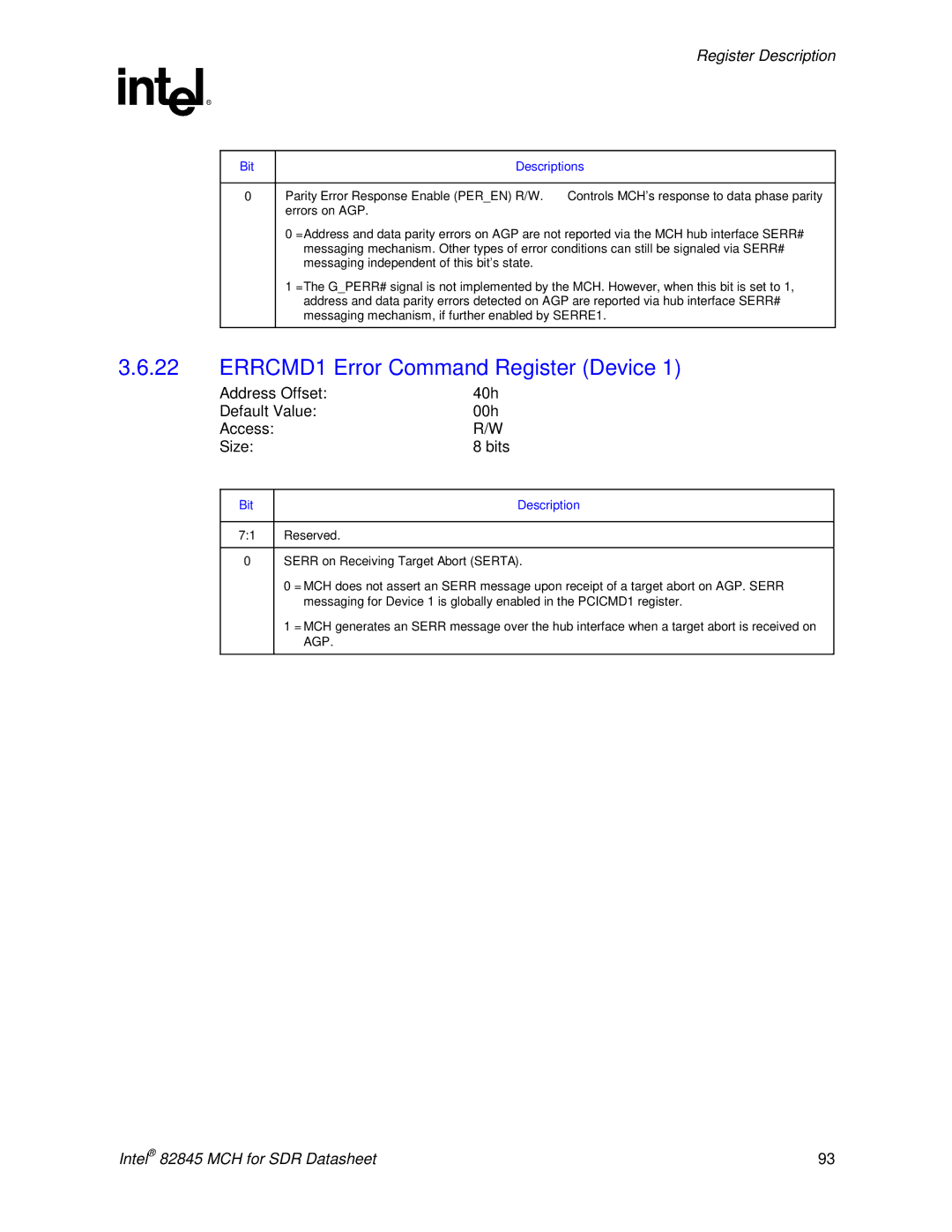

3.6.22ERRCMD1—Error Command Register (Device 1)

Address Offset: | 40h | |

Default Value: | 00h | |

Access: |

| R/W |

Size: |

| 8 bits |

|

|

|

Bit |

| Description |

|

|

|

7:1 | Reserved. |

|

|

| |

0 | SERR on Receiving Target Abort (SERTA). | |

| 0 = MCH does not assert an SERR message upon receipt of a target abort on AGP. SERR | |

| messaging for Device 1 is globally enabled in the PCICMD1 register. | |

| 1 = MCH generates an SERR message over the hub interface when a target abort is received on | |

| AGP. |

|

|

|

|

Intel® 82845 MCH for SDR Datasheet | 93 |