Register Description

R

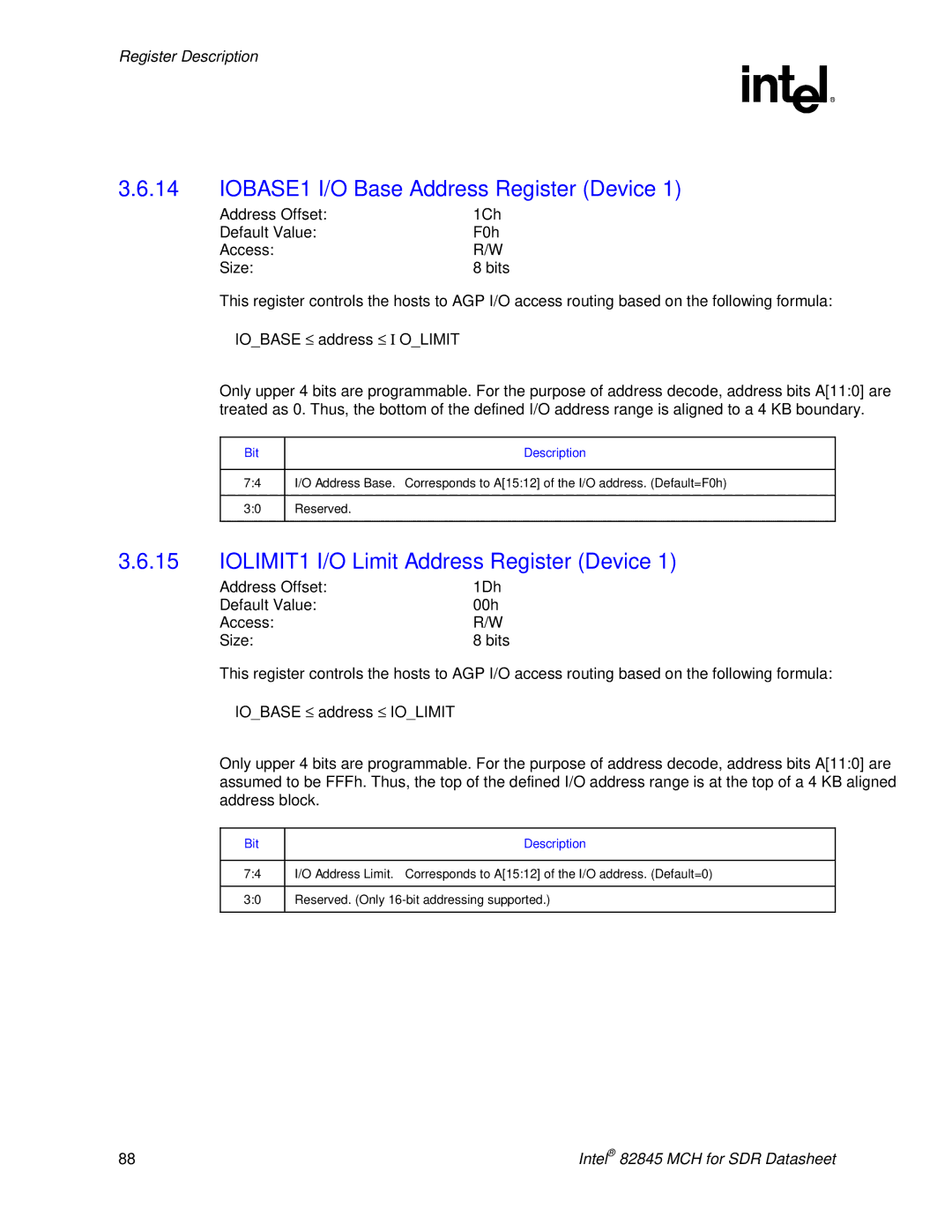

3.6.14IOBASE1—I/O Base Address Register (Device 1)

Address Offset: | 1Ch |

Default Value: | F0h |

Access: | R/W |

Size: | 8 bits |

This register controls the hosts to AGP I/O access routing based on the following formula:

IO_BASE ≤ address ≤ Ι O_LIMIT

Only upper 4 bits are programmable. For the purpose of address decode, address bits A[11:0] are treated as 0. Thus, the bottom of the defined I/O address range is aligned to a 4 KB boundary.

Bit | Description |

|

|

7:4 | I/O Address Base. Corresponds to A[15:12] of the I/O address. (Default=F0h) |

|

|

3:0 | Reserved. |

|

|

3.6.15IOLIMIT1—I/O Limit Address Register (Device 1)

Address Offset: | 1Dh |

Default Value: | 00h |

Access: | R/W |

Size: | 8 bits |

This register controls the hosts to AGP I/O access routing based on the following formula:

IO_BASE ≤ address ≤ IO_LIMIT

Only upper 4 bits are programmable. For the purpose of address decode, address bits A[11:0] are assumed to be FFFh. Thus, the top of the defined I/O address range is at the top of a 4 KB aligned address block.

Bit | Description |

|

|

7:4 | I/O Address Limit. Corresponds to A[15:12] of the I/O address. (Default=0) |

|

|

3:0 | Reserved. (Only |

|

|

88 | Intel® 82845 MCH for SDR Datasheet |