Introduction

R

1.4.5Hub Interface

The

•Interrupt related messages

•Power management events as messages

•SMI, SCI, and SERR error indication messages

It is assumed that the hub interface is always connected to an ICH2.

1.4.6Intel® MCH Clocking

The MCH has the following clock input pins:

•Differential BCLK for the host interface

•66 MHz clock input for the AGP and hub interface

Clock synthesizer chip(s) generate the system host clocks, AGP and hub interface clocks, and PCI clocks. The system bus target speed is 400 MHz. The MCH does not require any relationship between the HCLKIN host clock and the 66 MHz clock generated for AGP and the hub interface; they are asynchronous to each other. The AGP and hub interface runs at a constant 66 MHz base frequency. The hub interface runs at 4x. AGP transfers can be 1x, 2x, or 4x. Table 5 indicates the supported frequency ratios between the various interfaces.

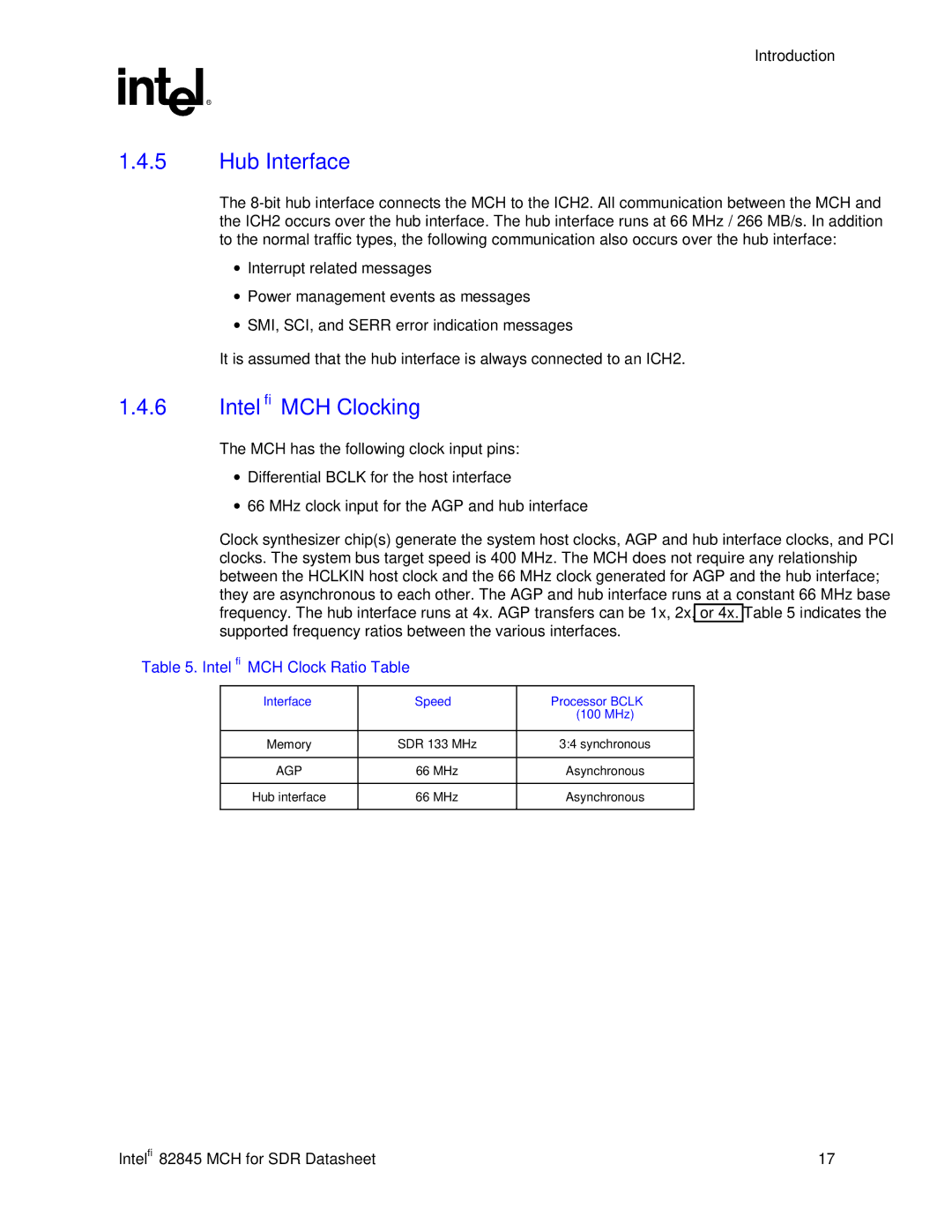

Table 5. Intel® MCH Clock Ratio Table

Interface | Speed | Processor BCLK |

|

| (100 MHz) |

|

|

|

Memory | SDR 133 MHz | 3:4 synchronous |

|

|

|

AGP | 66 MHz | Asynchronous |

|

|

|

Hub interface | 66 MHz | Asynchronous |

|

|

|

Intel® 82845 MCH for SDR Datasheet | 17 |