Register Description

R

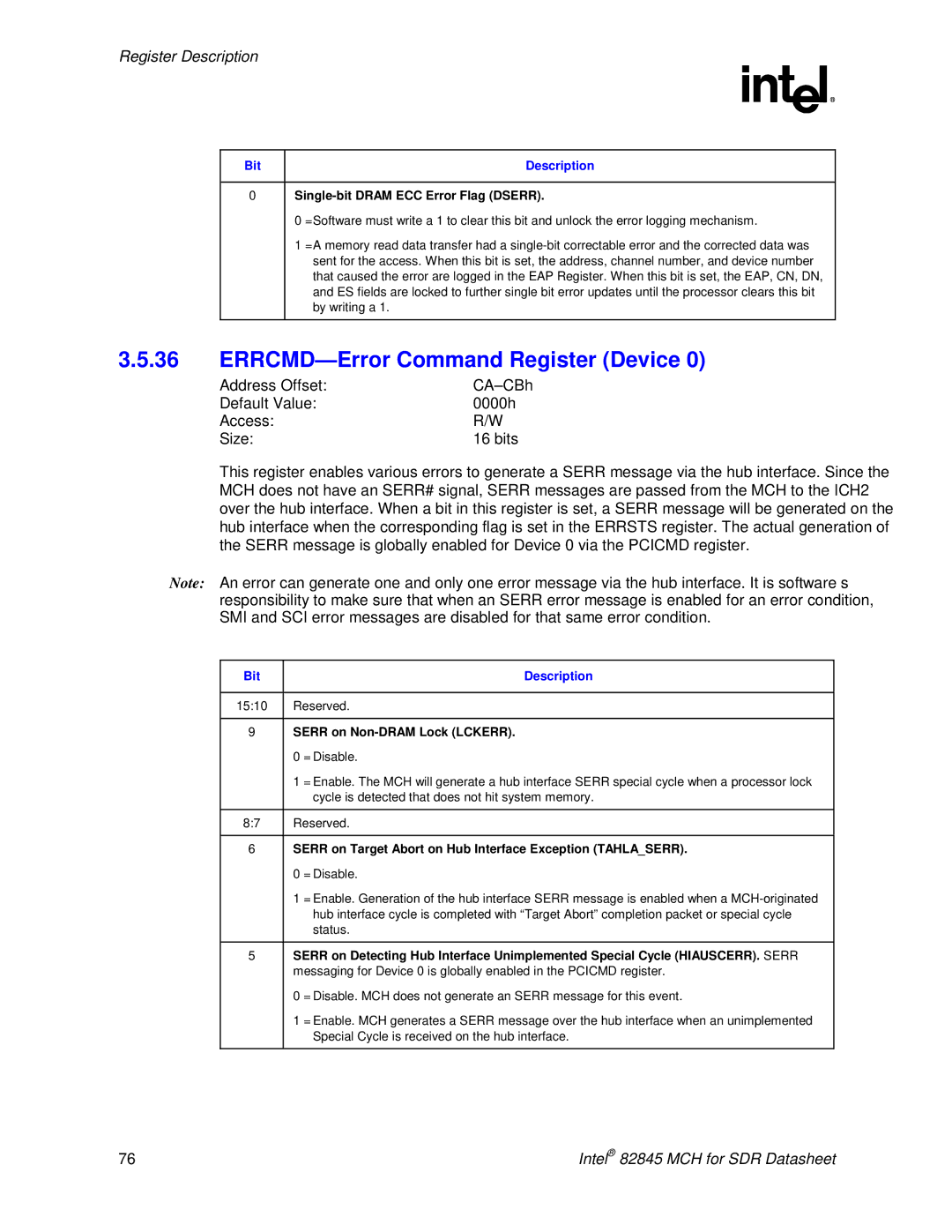

Bit |

| Description |

|

| |

0 |

| |

| 0 | =Software must write a 1 to clear this bit and unlock the error logging mechanism. |

| 1 | =A memory read data transfer had a |

|

| sent for the access. When this bit is set, the address, channel number, and device number |

|

| that caused the error are logged in the EAP Register. When this bit is set, the EAP, CN, DN, |

|

| and ES fields are locked to further single bit error updates until the processor clears this bit |

|

| by writing a 1. |

|

|

|

3.5.36ERRCMD—Error Command Register (Device 0)

Address Offset: |

|

Default Value: | 0000h |

Access: | R/W |

Size: | 16 bits |

This register enables various errors to generate a SERR message via the hub interface. Since the MCH does not have an SERR# signal, SERR messages are passed from the MCH to the ICH2 over the hub interface. When a bit in this register is set, a SERR message will be generated on the hub interface when the corresponding flag is set in the ERRSTS register. The actual generation of the SERR message is globally enabled for Device 0 via the PCICMD register.

Note: An error can generate one and only one error message via the hub interface. It is software’s responsibility to make sure that when an SERR error message is enabled for an error condition, SMI and SCI error messages are disabled for that same error condition.

Bit |

| Description |

|

| |

15:10 | Reserved. | |

|

| |

9 | SERR on | |

| 0 | = Disable. |

| 1 | = Enable. The MCH will generate a hub interface SERR special cycle when a processor lock |

|

| cycle is detected that does not hit system memory. |

|

| |

8:7 | Reserved. | |

|

| |

6 | SERR on Target Abort on Hub Interface Exception (TAHLA_SERR). | |

| 0 | = Disable. |

| 1 | = Enable. Generation of the hub interface SERR message is enabled when a |

|

| hub interface cycle is completed with “Target Abort” completion packet or special cycle |

|

| status. |

|

| |

5 | SERR on Detecting Hub Interface Unimplemented Special Cycle (HIAUSCERR). SERR | |

| messaging for Device 0 is globally enabled in the PCICMD register. | |

| 0 | = Disable. MCH does not generate an SERR message for this event. |

| 1 | = Enable. MCH generates a SERR message over the hub interface when an unimplemented |

|

| Special Cycle is received on the hub interface. |

|

|

|

76 | Intel® 82845 MCH for SDR Datasheet |