MPCBL0010

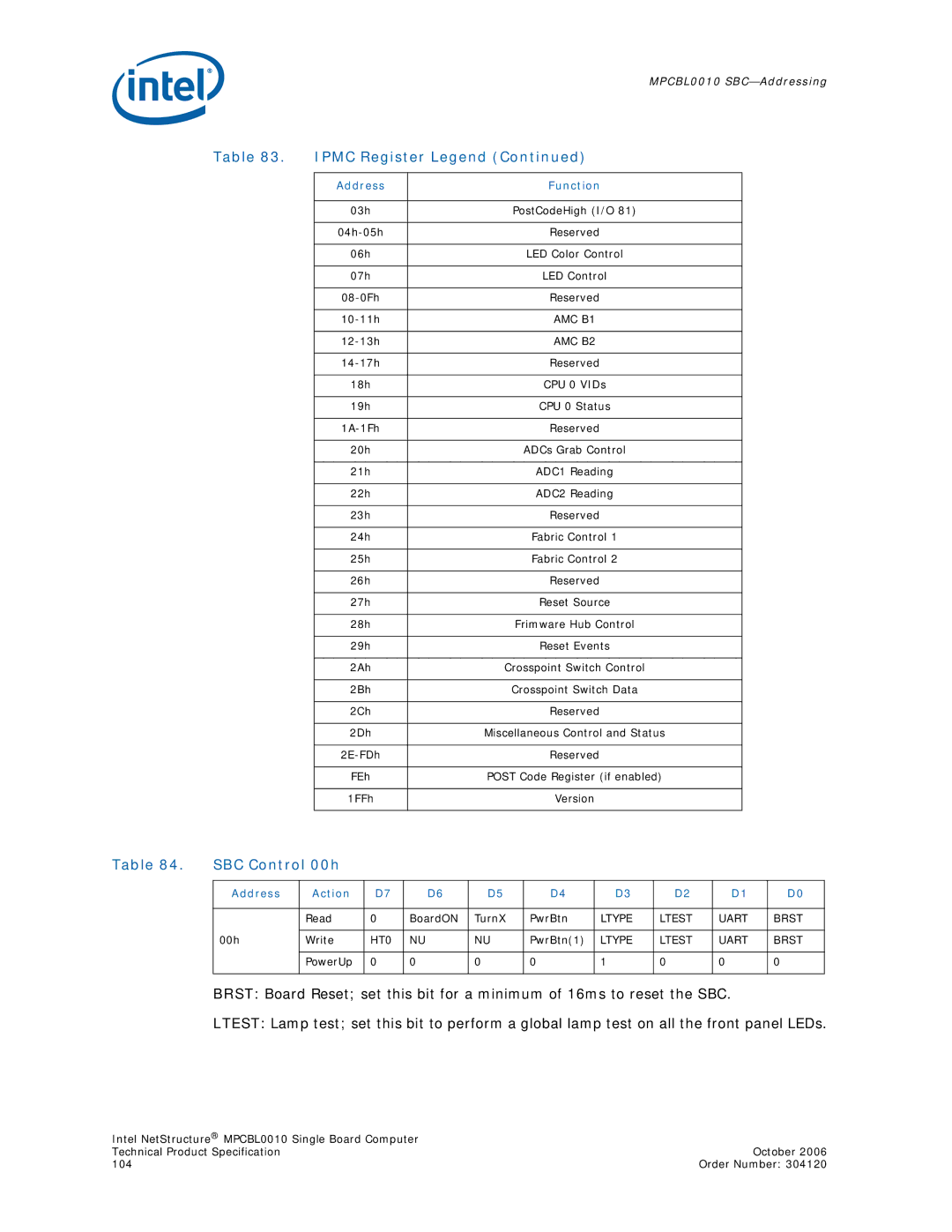

Table 83. | IPMC Register Legend (Continued) | |

|

|

|

| Address | Function |

|

|

|

| 03h | PostCodeHigh (I/O 81) |

|

|

|

| Reserved | |

|

|

|

| 06h | LED Color Control |

|

|

|

| 07h | LED Control |

|

|

|

| Reserved | |

|

|

|

| AMC B1 | |

|

|

|

| AMC B2 | |

|

|

|

| Reserved | |

|

|

|

| 18h | CPU 0 VIDs |

|

|

|

| 19h | CPU 0 Status |

|

|

|

| Reserved | |

|

|

|

| 20h | ADCs Grab Control |

|

|

|

| 21h | ADC1 Reading |

|

|

|

| 22h | ADC2 Reading |

|

|

|

| 23h | Reserved |

|

|

|

| 24h | Fabric Control 1 |

|

|

|

| 25h | Fabric Control 2 |

|

|

|

| 26h | Reserved |

|

|

|

| 27h | Reset Source |

|

|

|

| 28h | Frimware Hub Control |

|

|

|

| 29h | Reset Events |

|

|

|

| 2Ah | Crosspoint Switch Control |

|

|

|

| 2Bh | Crosspoint Switch Data |

|

|

|

| 2Ch | Reserved |

|

|

|

| 2Dh | Miscellaneous Control and Status |

|

|

|

| Reserved | |

|

|

|

| FEh | POST Code Register (if enabled) |

|

|

|

| 1FFh | Version |

|

|

|

Table 84. | SBC Control 00h |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| Address | Action | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

|

|

|

|

|

| Read | 0 | BoardON | TurnX | PwrBtn | LTYPE | LTEST | UART | BRST |

|

|

|

|

|

|

|

|

|

|

|

| 00h | Write | HT0 | NU | NU | PwrBtn(1) | LTYPE | LTEST | UART | BRST |

|

|

|

|

|

|

|

|

|

|

|

|

| PowerUp | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

|

BRST: Board Reset; set this bit for a minimum of 16ms to reset the SBC.

LTEST: Lamp test; set this bit to perform a global lamp test on all the front panel LEDs.

Intel NetStructure® MPCBL0010 Single Board Computer |

|

Technical Product Specification | October 2006 |

104 | Order Number: 304120 |