MPCBL0010

Main Advanced PCIPnP Boot Security Chipset Exit

NorthBridge Configuration

Spread Spectrum Clocking

Mode

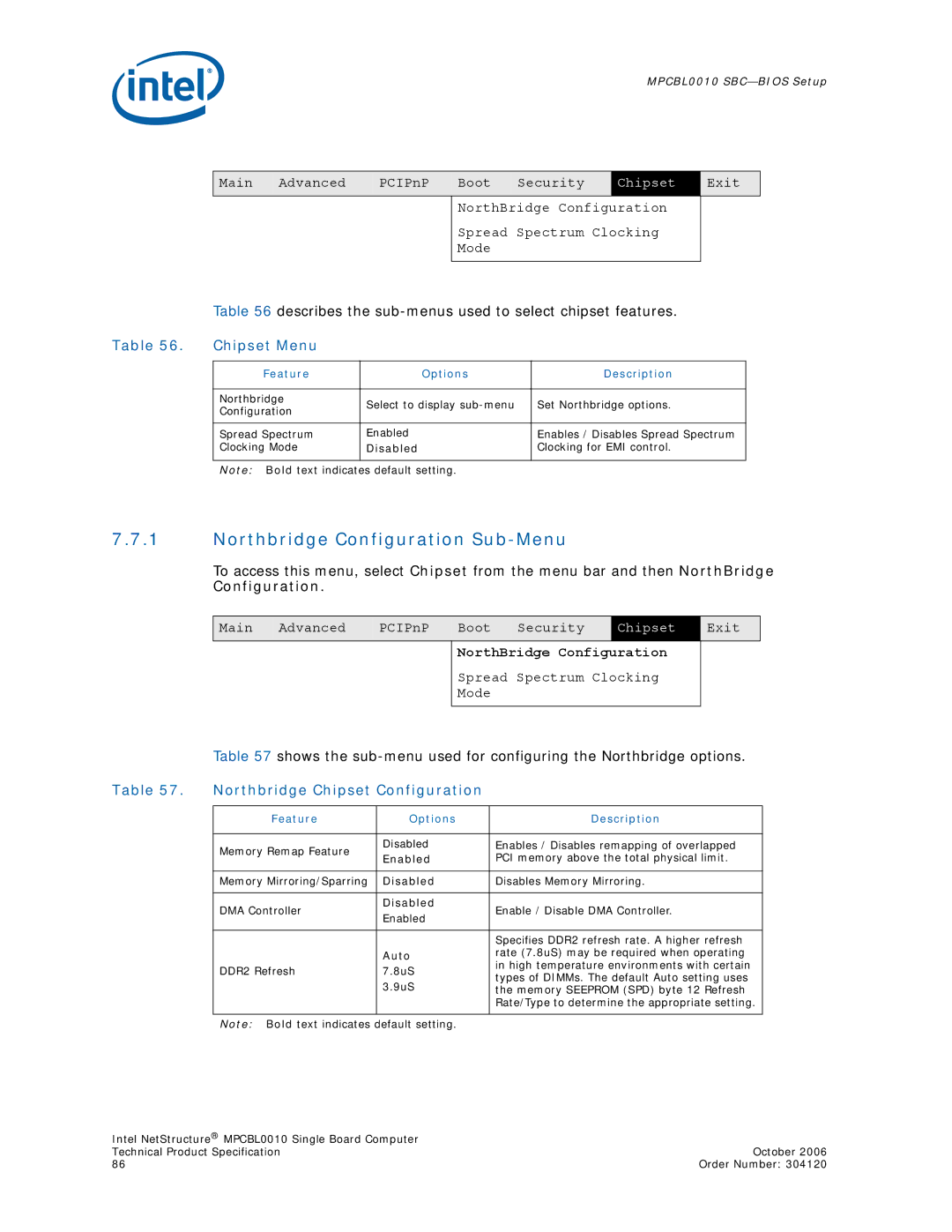

Table 56 describes the sub-menus used to select chipset features.

Table 56. | Chipset Menu |

|

|

|

|

|

|

| Feature | Options | Description |

|

|

|

|

| Northbridge | Select to display | Set Northbridge options. |

| Configuration | ||

|

|

| |

|

|

|

|

| Spread Spectrum | Enabled | Enables / Disables Spread Spectrum |

| Clocking Mode | Disabled | Clocking for EMI control. |

|

|

|

|

Note: Bold text indicates default setting.

7.7.1Northbridge Configuration Sub-Menu

To access this menu, select Chipset from the menu bar and then NorthBridge Configuration.

Main Advanced PCIPnP Boot Security Chipset Exit

NorthBridge Configuration

Spread Spectrum Clocking

Mode

Table 57 shows the

Table 57. | Northbridge Chipset Configuration |

| |

|

|

|

|

| Feature | Options | Description |

|

|

|

|

| Memory Remap Feature | Disabled | Enables / Disables remapping of overlapped |

| Enabled | PCI memory above the total physical limit. | |

|

| ||

|

|

|

|

| Memory Mirroring/Sparring | Disabled | Disables Memory Mirroring. |

|

|

|

|

| DMA Controller | Disabled | Enable / Disable DMA Controller. |

| Enabled | ||

|

|

| |

|

|

|

|

|

|

| Specifies DDR2 refresh rate. A higher refresh |

|

| Auto | rate (7.8uS) may be required when operating |

| DDR2 Refresh | 7.8uS | in high temperature environments with certain |

| types of DIMMs. The default Auto setting uses | ||

|

| 3.9uS | |

|

| the memory SEEPROM (SPD) byte 12 Refresh | |

|

|

| Rate/Type to determine the appropriate setting. |

|

|

|

|

Note: Bold text indicates default setting.

Intel NetStructure® MPCBL0010 Single Board Computer |

|

Technical Product Specification | October 2006 |

86 | Order Number: 304120 |