BIOS

Main | Advanced | PCIPnP Boot Security | Chipset | Exit |

Remote Access Configuration

IPMI Configuration

USB Configuration

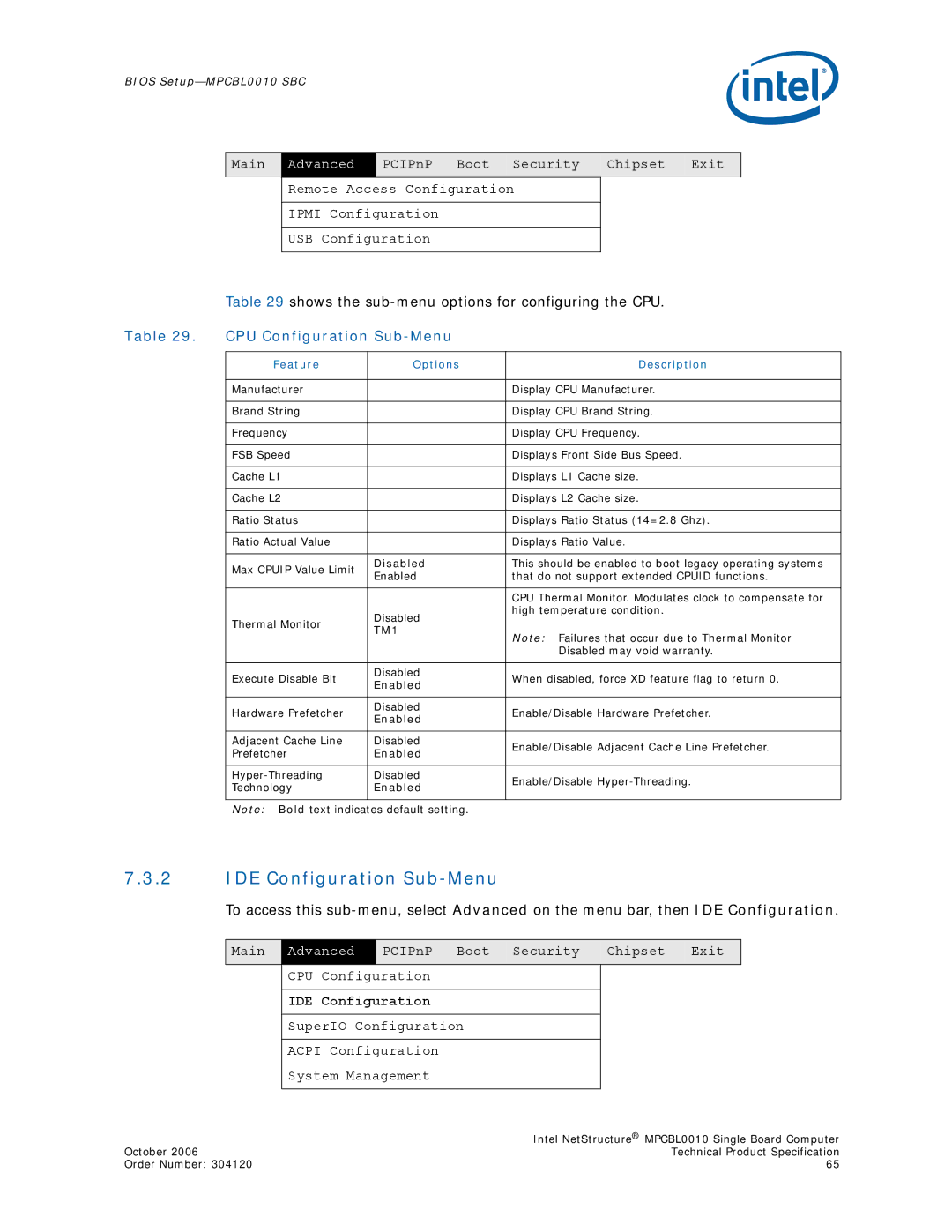

Table 29 shows the sub-menu options for configuring the CPU.

Table 29. | CPU Configuration |

| |

|

|

|

|

| Feature | Options | Description |

|

|

|

|

| Manufacturer |

| Display CPU Manufacturer. |

|

|

|

|

| Brand String |

| Display CPU Brand String. |

|

|

|

|

| Frequency |

| Display CPU Frequency. |

|

|

|

|

| FSB Speed |

| Displays Front Side Bus Speed. |

|

|

|

|

| Cache L1 |

| Displays L1 Cache size. |

|

|

|

|

| Cache L2 |

| Displays L2 Cache size. |

|

|

|

|

| Ratio Status |

| Displays Ratio Status (14=2.8 Ghz). |

|

|

|

|

| Ratio Actual Value |

| Displays Ratio Value. |

|

|

|

|

| Max CPUIP Value Limit | Disabled | This should be enabled to boot legacy operating systems |

| Enabled | that do not support extended CPUID functions. | |

|

| ||

|

|

|

|

|

|

| CPU Thermal Monitor. Modulates clock to compensate for |

|

| Disabled | high temperature condition. |

| Thermal Monitor |

| |

| TM1 |

| |

|

| Note: Failures that occur due to Thermal Monitor | |

|

|

| |

|

|

| Disabled may void warranty. |

|

|

|

|

| Execute Disable Bit | Disabled | When disabled, force XD feature flag to return 0. |

| Enabled | ||

|

|

| |

|

|

|

|

| Hardware Prefetcher | Disabled | Enable/Disable Hardware Prefetcher. |

| Enabled | ||

|

|

| |

|

|

|

|

| Adjacent Cache Line | Disabled | Enable/Disable Adjacent Cache Line Prefetcher. |

| Prefetcher | Enabled | |

|

| ||

|

|

|

|

| Disabled | Enable/Disable | |

| Technology | Enabled | |

|

| ||

|

|

|

|

Note: Bold text indicates default setting.

7.3.2IDE Configuration Sub-Menu

To access this

Main | Advanced | PCIPnP Boot Security | Chipset | Exit |

| CPU Configuration |

|

| |

| IDE Configuration |

|

| |

| SuperIO Configuration |

|

| |

| ACPI Configuration |

|

| |

| System Management |

|

| |

| Intel NetStructure® MPCBL0010 Single Board Computer |

October 2006 | Technical Product Specification |

Order Number: 304120 | 65 |