MPCBL0010

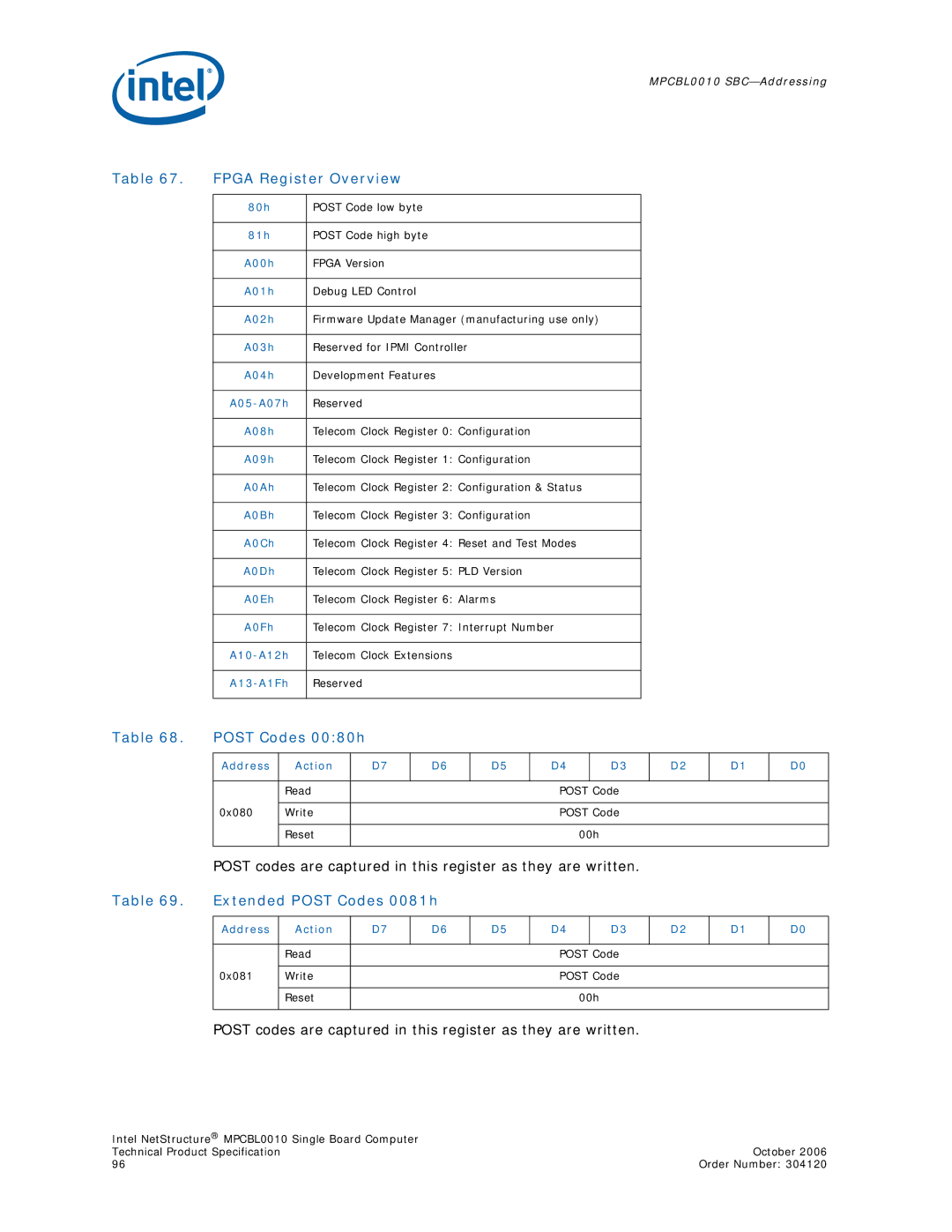

Table 67. | FPGA Register Overview | |

|

|

|

| 80h | POST Code low byte |

|

|

|

| 81h | POST Code high byte |

|

|

|

| A00h | FPGA Version |

|

|

|

| A01h | Debug LED Control |

|

|

|

| A02h | Firmware Update Manager (manufacturing use only) |

|

|

|

| A03h | Reserved for IPMI Controller |

|

|

|

| A04h | Development Features |

|

|

|

| Reserved | |

|

|

|

| A08h | Telecom Clock Register 0: Configuration |

|

|

|

| A09h | Telecom Clock Register 1: Configuration |

|

|

|

| A0Ah | Telecom Clock Register 2: Configuration & Status |

|

|

|

| A0Bh | Telecom Clock Register 3: Configuration |

|

|

|

| A0Ch | Telecom Clock Register 4: Reset and Test Modes |

|

|

|

| A0Dh | Telecom Clock Register 5: PLD Version |

|

|

|

| A0Eh | Telecom Clock Register 6: Alarms |

|

|

|

| A0Fh | Telecom Clock Register 7: Interrupt Number |

|

|

|

| Telecom Clock Extensions | |

|

|

|

| Reserved | |

|

|

|

Table 68. | POST Codes 00:80h |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| Address | Action |

| D7 | D6 | D5 | D4 |

| D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

|

|

|

|

| |

|

| Read |

|

|

|

| POST Code |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| ||

| 0x080 | Write |

|

|

|

| POST Code |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

|

| Reset |

|

|

|

|

| 00h |

|

|

| |

|

|

|

|

|

|

|

|

|

|

| ||

| POST codes are captured in this register as they are written. |

|

|

| ||||||||

Table 69. | Extended POST Codes 0081h |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| Address | Action | D7 | D6 | D5 | D4 |

| D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

|

|

|

| |

|

| Read |

|

|

| POST Code |

|

|

| ||

|

|

|

|

|

|

|

|

|

| ||

| 0x081 | Write |

|

|

| POST Code |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

|

| Reset |

|

|

|

| 00h |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

POST codes are captured in this register as they are written.

Intel NetStructure® MPCBL0010 Single Board Computer |

|

Technical Product Specification | October 2006 |

96 | Order Number: 304120 |