MPCBL0010

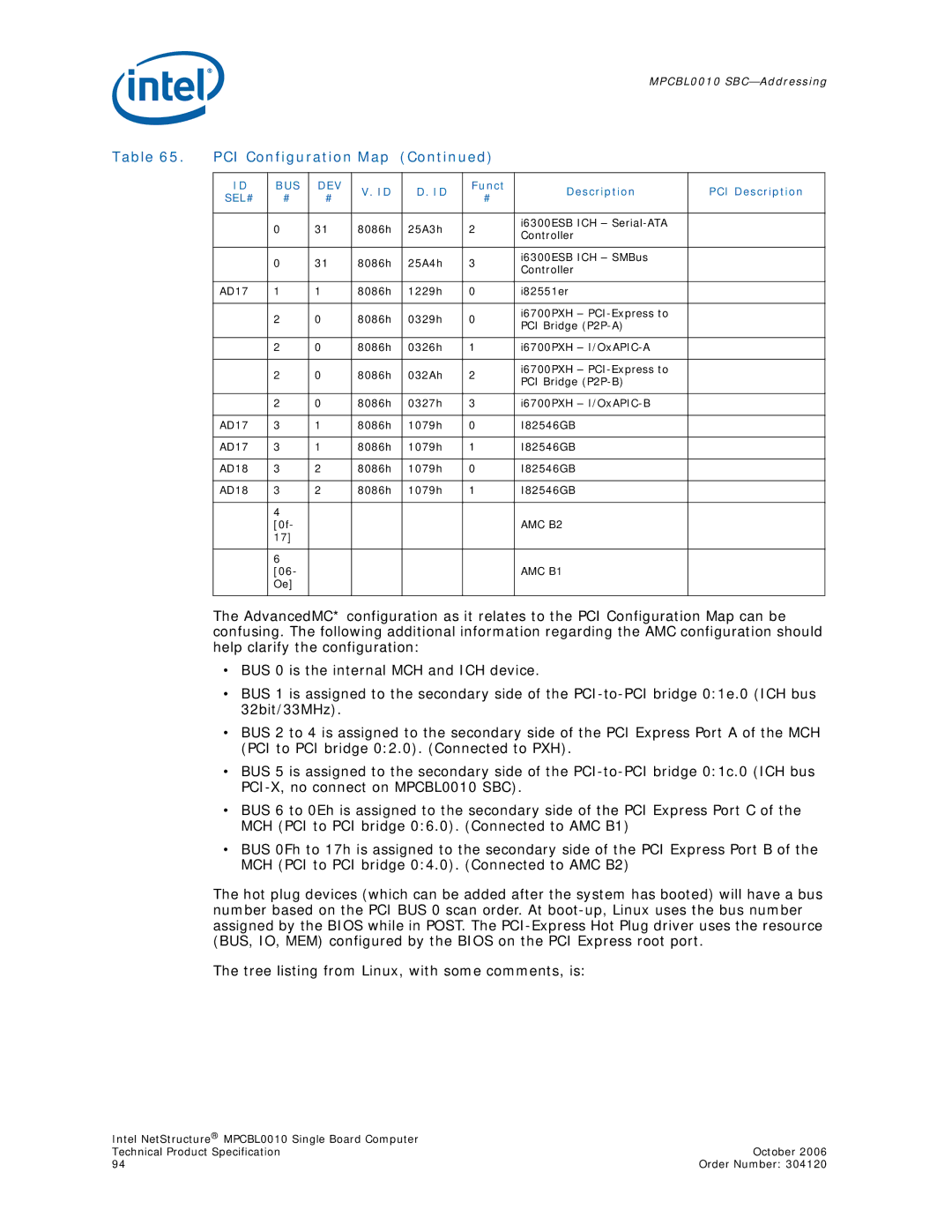

Table 65. | PCI Configuration Map (Continued) |

|

| |||||

|

|

|

|

|

|

|

|

|

| ID | BUS | DEV | V. ID | D. ID | Funct | Description | PCI Description |

| SEL# | # | # | # | ||||

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| 0 | 31 | 8086h | 25A3h | 2 | i6300ESB ICH – |

|

|

| Controller |

| |||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 0 | 31 | 8086h | 25A4h | 3 | i6300ESB ICH – SMBus |

|

|

| Controller |

| |||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| AD17 | 1 | 1 | 8086h | 1229h | 0 | i82551er |

|

|

|

|

|

|

|

|

|

|

|

| 2 | 0 | 8086h | 0329h | 0 | i6700PXH – |

|

|

| PCI Bridge |

| |||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 2 | 0 | 8086h | 0326h | 1 | i6700PXH – |

|

|

|

|

|

|

|

|

|

|

|

| 2 | 0 | 8086h | 032Ah | 2 | i6700PXH – |

|

|

| PCI Bridge |

| |||||

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 2 | 0 | 8086h | 0327h | 3 | i6700PXH – |

|

|

|

|

|

|

|

|

|

|

| AD17 | 3 | 1 | 8086h | 1079h | 0 | I82546GB |

|

|

|

|

|

|

|

|

|

|

| AD17 | 3 | 1 | 8086h | 1079h | 1 | I82546GB |

|

|

|

|

|

|

|

|

|

|

| AD18 | 3 | 2 | 8086h | 1079h | 0 | I82546GB |

|

|

|

|

|

|

|

|

|

|

| AD18 | 3 | 2 | 8086h | 1079h | 1 | I82546GB |

|

|

|

|

|

|

|

|

|

|

|

| 4 |

|

|

|

|

|

|

|

| [0f- |

|

|

|

| AMC B2 |

|

|

| 17] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 6 |

|

|

|

|

|

|

|

| [06- |

|

|

|

| AMC B1 |

|

|

| Oe] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The AdvancedMC* configuration as it relates to the PCI Configuration Map can be confusing. The following additional information regarding the AMC configuration should help clarify the configuration:

•BUS 0 is the internal MCH and ICH device.

•BUS 1 is assigned to the secondary side of the

•BUS 2 to 4 is assigned to the secondary side of the PCI Express Port A of the MCH (PCI to PCI bridge 0:2.0). (Connected to PXH).

•BUS 5 is assigned to the secondary side of the

•BUS 6 to 0Eh is assigned to the secondary side of the PCI Express Port C of the MCH (PCI to PCI bridge 0:6.0). (Connected to AMC B1)

•BUS 0Fh to 17h is assigned to the secondary side of the PCI Express Port B of the MCH (PCI to PCI bridge 0:4.0). (Connected to AMC B2)

The hot plug devices (which can be added after the system has booted) will have a bus number based on the PCI BUS 0 scan order. At

The tree listing from Linux, with some comments, is:

Intel NetStructure® MPCBL0010 Single Board Computer |

|

Technical Product Specification | October 2006 |

94 | Order Number: 304120 |