SSC1: Special Serial Connection bit 1

SSC1/SSC0:

01:Float the FW_RXD pin

10:Connect FW_RXD and FW_TXD to an

00:Connect B1 to ICH UART1

PCB: PCB version.

These bits define special connections between serial devices that are meaningless under normal operation. They are for development and/or manufacturing facilities. Leave these bits in their default state for normal operation.

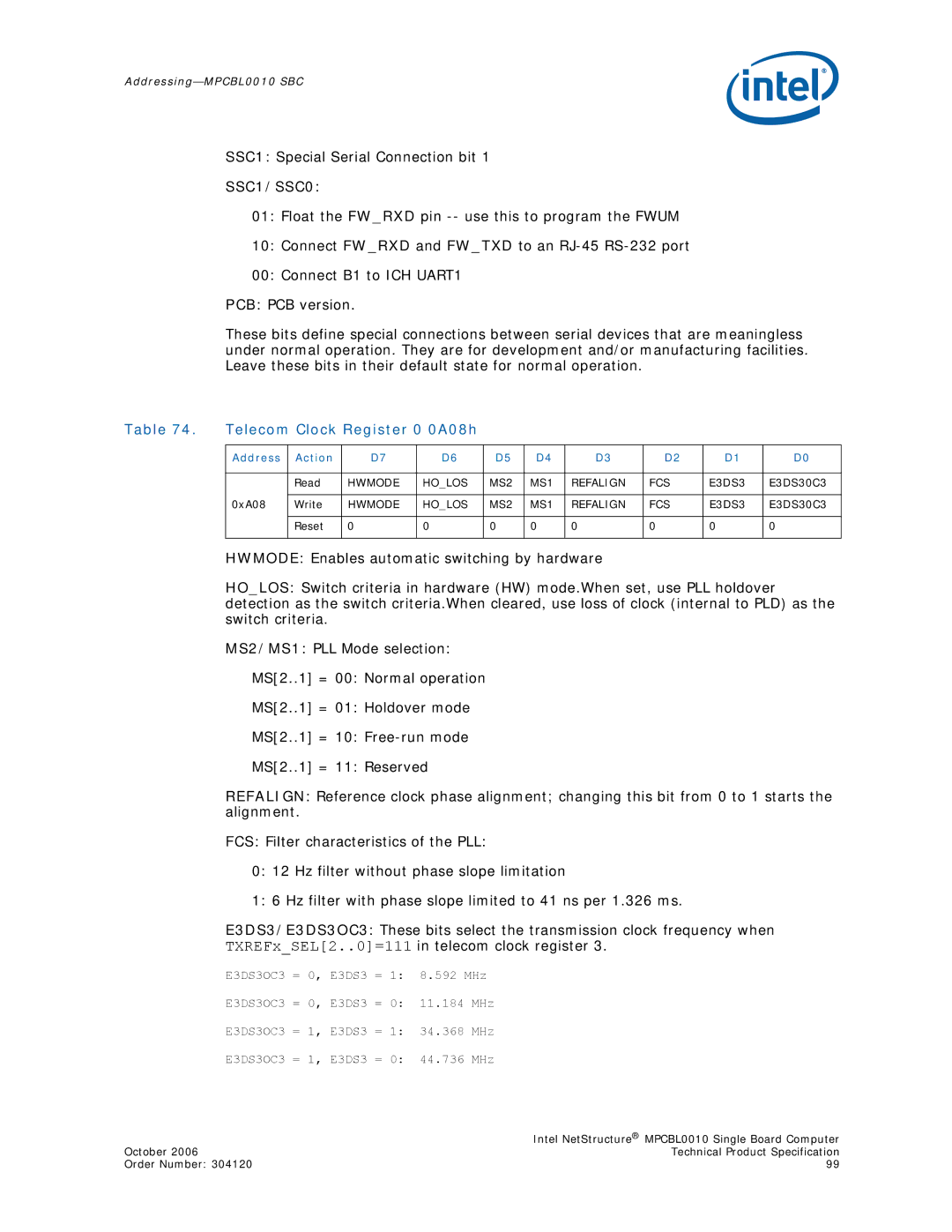

Table 74. | Telecom Clock Register 0 0A08h |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| Address | Action | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

|

|

|

|

|

| Read | HWMODE | HO_LOS | MS2 | MS1 | REFALIGN | FCS | E3DS3 | E3DS30C3 |

|

|

|

|

|

|

|

|

|

|

|

| 0xA08 | Write | HWMODE | HO_LOS | MS2 | MS1 | REFALIGN | FCS | E3DS3 | E3DS30C3 |

|

|

|

|

|

|

|

|

|

|

|

|

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

|

HWMODE: Enables automatic switching by hardware

HO_LOS: Switch criteria in hardware (HW) mode.When set, use PLL holdover detection as the switch criteria.When cleared, use loss of clock (internal to PLD) as the switch criteria.

MS2/MS1: PLL Mode selection:

MS[2..1] = 00: Normal operation

MS[2..1] = 01: Holdover mode

MS[2..1] = 10:

MS[2..1] = 11: Reserved

REFALIGN: Reference clock phase alignment; changing this bit from 0 to 1 starts the alignment.

FCS: Filter characteristics of the PLL:

0:12 Hz filter without phase slope limitation

1:6 Hz filter with phase slope limited to 41 ns per 1.326 ms.

E3DS3/E3DS3OC3: These bits select the transmission clock frequency when TXREFx_SEL[2..0]=111 in telecom clock register 3.

E3DS3OC3 = 0, E3DS3 = 1: 8.592 MHz

E3DS3OC3 = 0, E3DS3 = 0: 11.184 MHz

E3DS3OC3 = 1, E3DS3 = 1: 34.368 MHz

E3DS3OC3 = 1, E3DS3 = 0: 44.736 MHz

| Intel NetStructure® MPCBL0010 Single Board Computer |

October 2006 | Technical Product Specification |

Order Number: 304120 | 99 |