Telecom

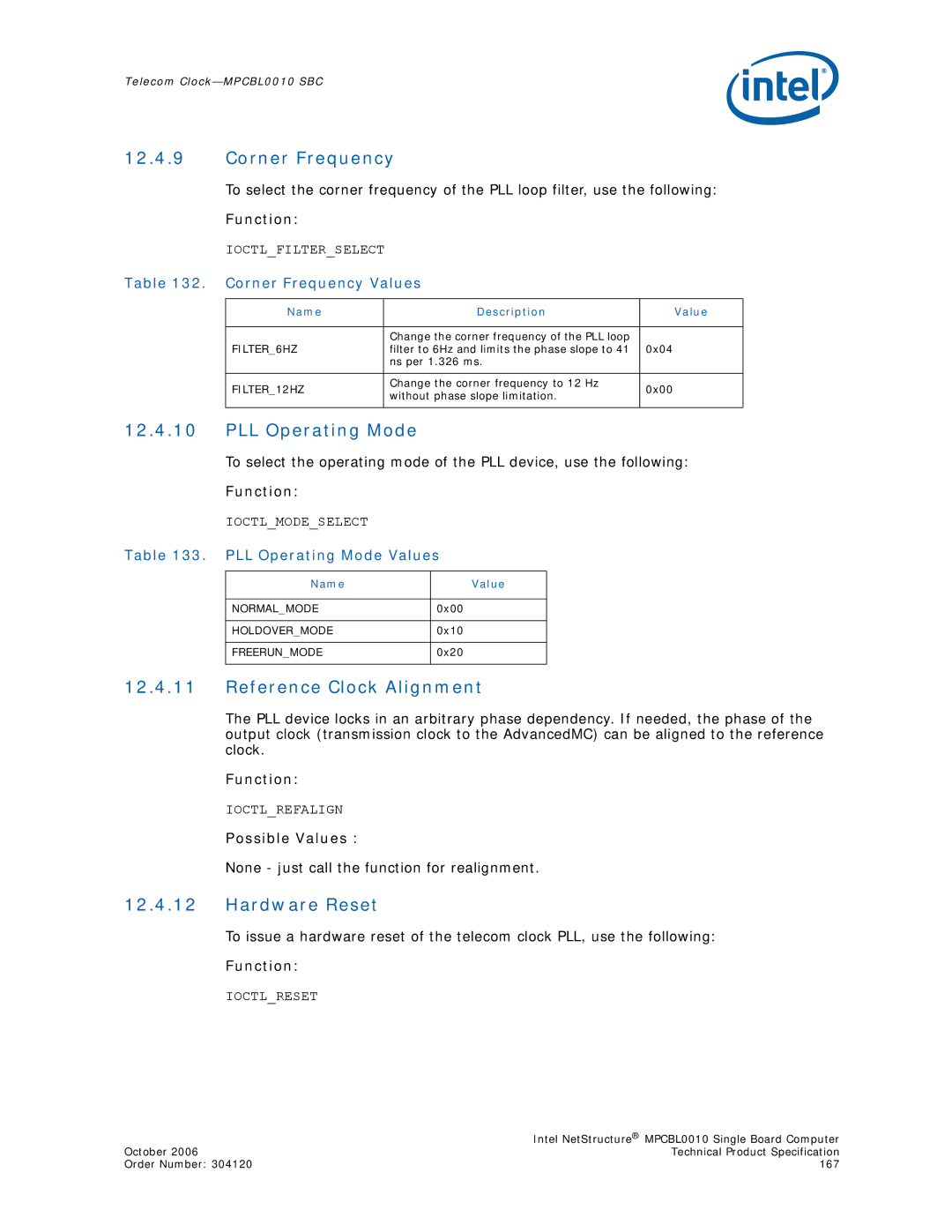

12.4.9Corner Frequency

To select the corner frequency of the PLL loop filter, use the following:

Function:

IOCTL_FILTER_SELECT

Table 132. Corner Frequency Values

Name | Description | Value | |

|

|

| |

| Change the corner frequency of the PLL loop |

| |

FILTER_6HZ | filter to 6Hz and limits the phase slope to 41 | 0x04 | |

| ns per 1.326 ms. |

| |

|

|

| |

FILTER_12HZ | Change the corner frequency to 12 Hz | 0x00 | |

without phase slope limitation. | |||

|

| ||

|

|

|

12.4.10PLL Operating Mode

To select the operating mode of the PLL device, use the following:

Function:

IOCTL_MODE_SELECT

Table 133. PLL Operating Mode Values

Name | Value |

|

|

NORMAL_MODE | 0x00 |

|

|

HOLDOVER_MODE | 0x10 |

|

|

FREERUN_MODE | 0x20 |

|

|

12.4.11Reference Clock Alignment

The PLL device locks in an arbitrary phase dependency. If needed, the phase of the output clock (transmission clock to the AdvancedMC) can be aligned to the reference clock.

Function:

IOCTL_REFALIGN

Possible Values :

None - just call the function for realignment.

12.4.12Hardware Reset

To issue a hardware reset of the telecom clock PLL, use the following:

Function:

IOCTL_RESET

| Intel NetStructure® MPCBL0010 Single Board Computer |

October 2006 | Technical Product Specification |

Order Number: 304120 | 167 |