MPCBL0010

initialized. The IPMC firmware defaults to no ACPI until this command is received with proper data in the request to indicate the operating system is either

10.11.6IPMB Link Sensor

The MPCBL0010 SBC provides two IPMB links to increase communication reliability to the shelf manager and other IPMI devices on the IPMB bus. These IPMB links work together for increased throughput where both buses are actively used for communication at any point. A request might be received over IPMB Bus A, and the response is sent over IPMB Bus B. Any requests that time out are retried on the redundant IPMB bus. In the event of any link state changes, the events are written to the SEL. The IPMC monitors the bus for any link failure and isolates itself from the bus if it detects that it is causing errors on the bus. Events are sent to signify the failure of a bus or, conversely, the recovery of a bus.

10.11.7FRU Hot Swap

The hot swap event message conveys the current state of the FRU, the previous state, and a cause of the state change as can be determined by the IPMC. Refer to the PICMG

3.0 specifications for further information about the hot swap state.

10.12Reset

The following sections describe the two types of reset requests and the boot relationships among them. The two types of reset requests available on the MPCBL0010 SBC are:

•Hard reset request (always results in a cold boot)

•Warm reset request (can result in either a warm or cold boot)

A hard reset request occurs whenever the processor Reset line is asserted and then deasserted. A soft reset occurs whenever an assertion occurs on the processor Init line. Whenever a soft reset request occurs, the BIOS checks two memory locations to determine whether to initiate a warm boot while leaving main memory intact or a cold boot that clears memory.

The reset button on the front panel is an input to the IPMC. There are also IPMI commands to reset the board and change power states through the software. However, the reset button is a last resort because the user must be physically present at the chassis to reset the board.

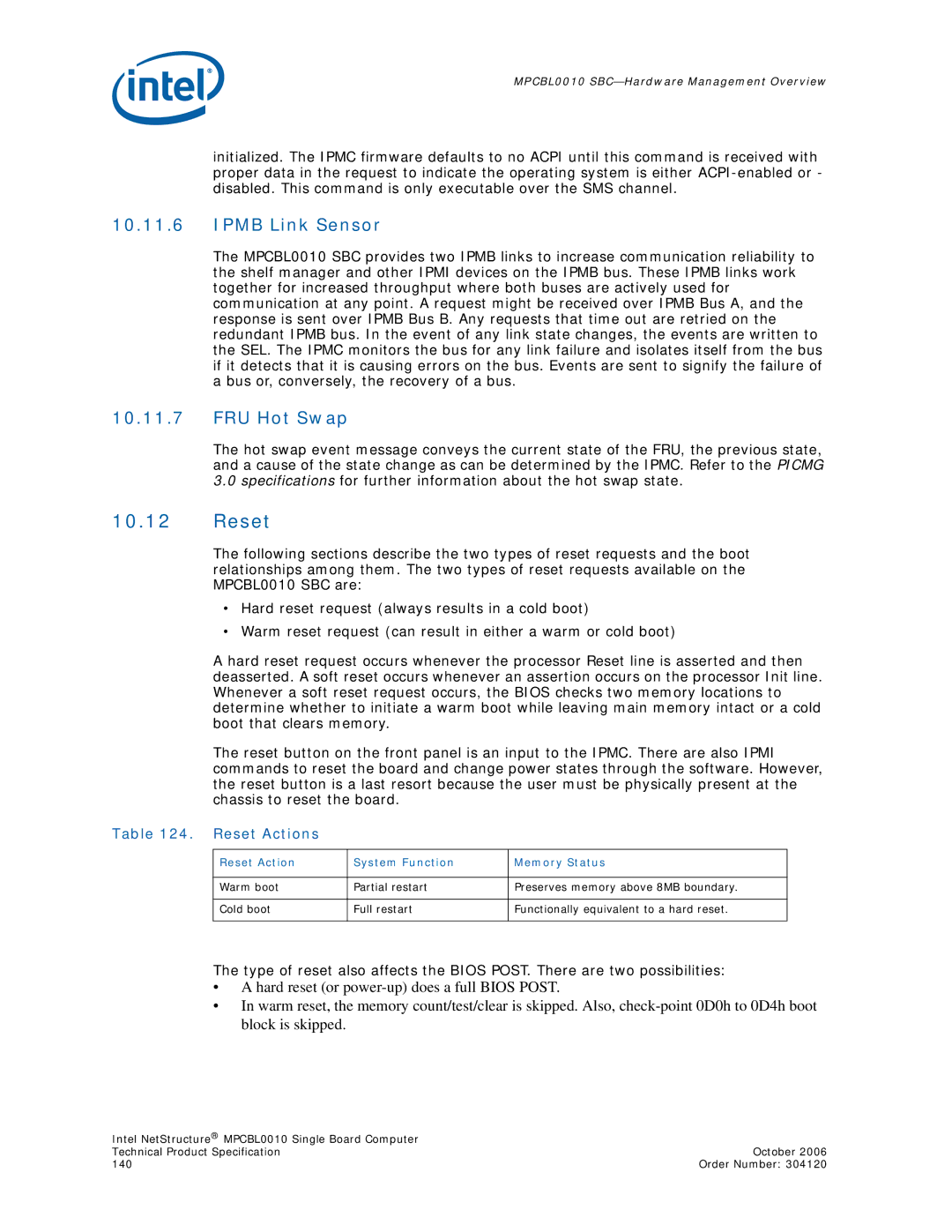

Table 124. Reset Actions

Reset Action | System Function | Memory Status |

|

|

|

Warm boot | Partial restart | Preserves memory above 8MB boundary. |

|

|

|

Cold boot | Full restart | Functionally equivalent to a hard reset. |

|

|

|

The type of reset also affects the BIOS POST. There are two possibilities:

•A hard reset (or

•In warm reset, the memory count/test/clear is skipped. Also,

Intel NetStructure® MPCBL0010 Single Board Computer |

|

Technical Product Specification | October 2006 |

140 | Order Number: 304120 |