Hardware Management

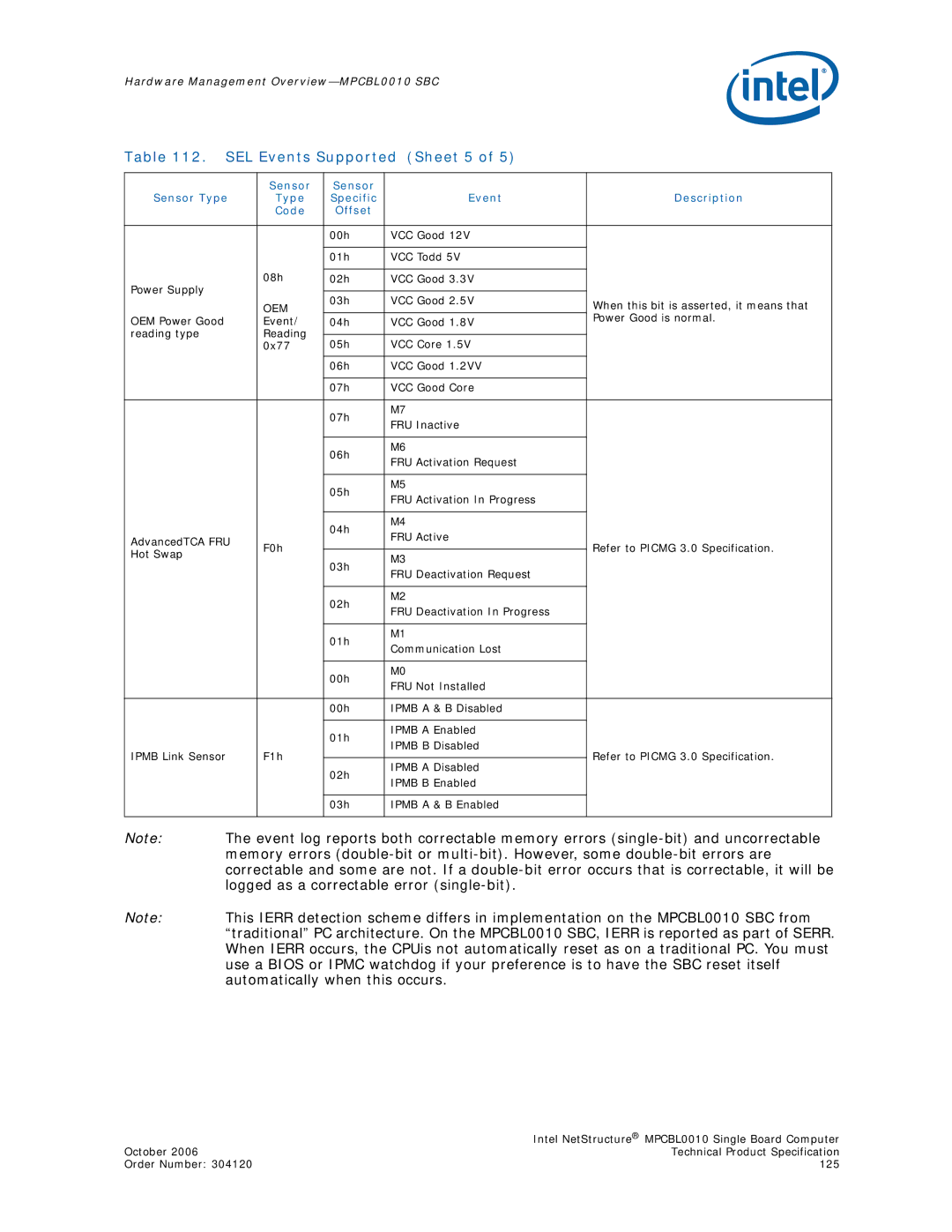

Table 112. SEL Events Supported (Sheet 5 of 5)

| Sensor | Sensor |

|

| |

Sensor Type | Type | Specific | Event | Description | |

| Code | Offset |

|

| |

|

|

|

|

| |

|

| 00h | VCC Good 12V |

| |

|

|

|

|

| |

|

| 01h | VCC Todd 5V |

| |

| 08h |

|

|

| |

Power Supply | 02h | VCC Good 3.3V |

| ||

|

|

|

| ||

OEM | 03h | VCC Good 2.5V | When this bit is asserted, it means that | ||

| |||||

|

|

| |||

OEM Power Good | Event/ |

|

| Power Good is normal. | |

04h | VCC Good 1.8V | ||||

reading type | Reading |

|

|

| |

05h | VCC Core 1.5V |

| |||

| 0x77 |

| |||

|

|

|

|

| |

|

| 06h | VCC Good 1.2VV |

| |

|

|

|

|

| |

|

| 07h | VCC Good Core |

| |

|

|

|

|

| |

|

| 07h | M7 |

| |

|

| FRU Inactive |

| ||

|

|

|

| ||

|

|

|

|

| |

|

| 06h | M6 |

| |

|

| FRU Activation Request |

| ||

|

|

|

| ||

|

|

|

|

| |

|

| 05h | M5 |

| |

|

| FRU Activation In Progress |

| ||

|

|

|

| ||

|

|

|

|

| |

|

| 04h | M4 |

| |

AdvancedTCA FRU |

| FRU Active |

| ||

F0h |

| Refer to PICMG 3.0 Specification. | |||

|

| ||||

Hot Swap | 03h | M3 | |||

|

| ||||

|

|

| |||

|

| FRU Deactivation Request |

| ||

|

|

|

| ||

|

|

|

|

| |

|

| 02h | M2 |

| |

|

| FRU Deactivation In Progress |

| ||

|

|

|

| ||

|

|

|

|

| |

|

| 01h | M1 |

| |

|

| Communication Lost |

| ||

|

|

|

| ||

|

|

|

|

| |

|

| 00h | M0 |

| |

|

| FRU Not Installed |

| ||

|

|

|

| ||

|

|

|

|

| |

|

| 00h | IPMB A & B Disabled |

| |

|

|

|

|

| |

|

| 01h | IPMB A Enabled |

| |

|

| IPMB B Disabled |

| ||

IPMB Link Sensor | F1h |

| Refer to PICMG 3.0 Specification. | ||

|

| ||||

02h | IPMB A Disabled | ||||

|

|

| |||

|

| IPMB B Enabled |

| ||

|

|

|

| ||

|

|

|

|

| |

|

| 03h | IPMB A & B Enabled |

| |

|

|

|

|

|

Note: The event log reports both correctable memory errors

Note: This IERR detection scheme differs in implementation on the MPCBL0010 SBC from “traditional” PC architecture. On the MPCBL0010 SBC, IERR is reported as part of SERR. When IERR occurs, the CPUis not automatically reset as on a traditional PC. You must use a BIOS or IPMC watchdog if your preference is to have the SBC reset itself automatically when this occurs.

| Intel NetStructure® MPCBL0010 Single Board Computer |

October 2006 | Technical Product Specification |

Order Number: 304120 | 125 |