MPCBL0010

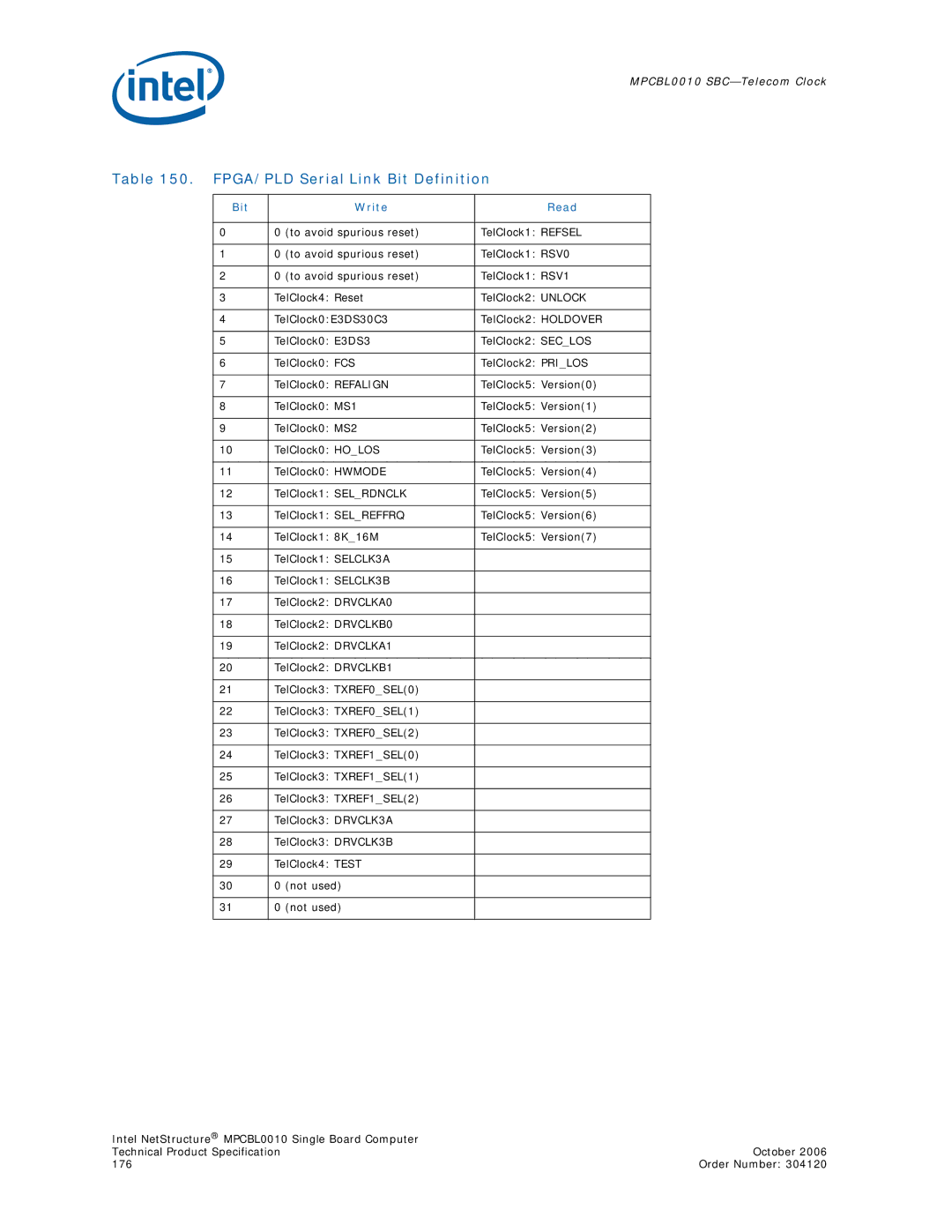

Table 150. FPGA/PLD Serial Link Bit Definition

Bit | Write | Read |

|

|

|

0 | 0 (to avoid spurious reset) | TelClock1: REFSEL |

|

|

|

1 | 0 (to avoid spurious reset) | TelClock1: RSV0 |

|

|

|

2 | 0 (to avoid spurious reset) | TelClock1: RSV1 |

|

|

|

3 | TelClock4: Reset | TelClock2: UNLOCK |

|

|

|

4 | TelClock0:E3DS30C3 | TelClock2: HOLDOVER |

|

|

|

5 | TelClock0: E3DS3 | TelClock2: SEC_LOS |

|

|

|

6 | TelClock0: FCS | TelClock2: PRI_LOS |

|

|

|

7 | TelClock0: REFALIGN | TelClock5: Version(0) |

|

|

|

8 | TelClock0: MS1 | TelClock5: Version(1) |

|

|

|

9 | TelClock0: MS2 | TelClock5: Version(2) |

|

|

|

10 | TelClock0: HO_LOS | TelClock5: Version(3) |

|

|

|

11 | TelClock0: HWMODE | TelClock5: Version(4) |

|

|

|

12 | TelClock1: SEL_RDNCLK | TelClock5: Version(5) |

|

|

|

13 | TelClock1: SEL_REFFRQ | TelClock5: Version(6) |

|

|

|

14 | TelClock1: 8K_16M | TelClock5: Version(7) |

|

|

|

15 | TelClock1: SELCLK3A |

|

|

|

|

16 | TelClock1: SELCLK3B |

|

|

|

|

17 | TelClock2: DRVCLKA0 |

|

|

|

|

18 | TelClock2: DRVCLKB0 |

|

|

|

|

19 | TelClock2: DRVCLKA1 |

|

|

|

|

20 | TelClock2: DRVCLKB1 |

|

|

|

|

21 | TelClock3: TXREF0_SEL(0) |

|

|

|

|

22 | TelClock3: TXREF0_SEL(1) |

|

|

|

|

23 | TelClock3: TXREF0_SEL(2) |

|

|

|

|

24 | TelClock3: TXREF1_SEL(0) |

|

|

|

|

25 | TelClock3: TXREF1_SEL(1) |

|

|

|

|

26 | TelClock3: TXREF1_SEL(2) |

|

|

|

|

27 | TelClock3: DRVCLK3A |

|

|

|

|

28 | TelClock3: DRVCLK3B |

|

|

|

|

29 | TelClock4: TEST |

|

|

|

|

30 | 0 (not used) |

|

|

|

|

31 | 0 (not used) |

|

|

|

|

Intel NetStructure® MPCBL0010 Single Board Computer |

|

Technical Product Specification | October 2006 |

176 | Order Number: 304120 |