MPCBL0010

0 = from first AdvancedMC module (AMC B1, CLKC)

1 = from second AdvancedMC module (AMC B2, CLKC).

8K_16M: This bit is valid only when the transmission clock is selected by setting TXREFx_SEL[2..0]=101 in the TelClock3 register.

Setting this bit selects the transmission clock frequency as 16.384 MHz Clearing this bit selects 8.0 kHz.

SEL_REFFRQ: Selects the reference frequency (8 k or 19.44 M):

0 = 8 kHz

1=19.44 MHz

SEL_REFFRQ: this bit controls the multiplexer that feeds clocks to the PLL:

0:PLL input clocks = CLK1A and CLK1B (8 kHz, per AdvancedTCA specification)

1:PLL input clocks = CLK2A and CLK2B (19.44 MHz, per AdvancedTCA specification).

SEL_RDNCLK: Setting this bit to the value of the formerly read REFSEL enables the switchover to the unused reference in the case of LOS for the actual reference.

REFSEL: Show the reference that is currently selected:

0:Primary reference

1:Secondary reference

RSV1/ RSV0: Reserved.

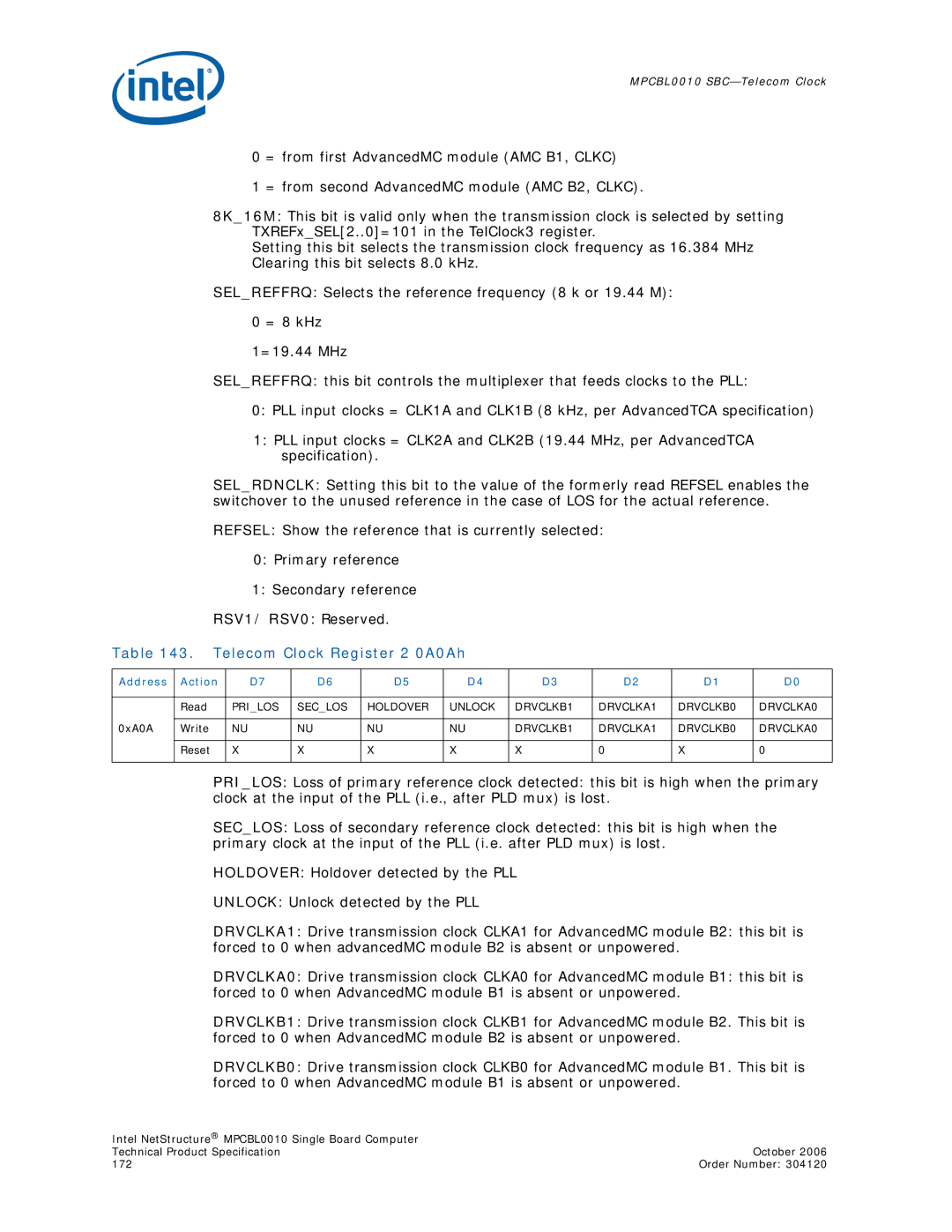

Table 143. Telecom Clock Register 2 0A0Ah

Address | Action | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

|

|

|

| Read | PRI_LOS | SEC_LOS | HOLDOVER | UNLOCK | DRVCLKB1 | DRVCLKA1 | DRVCLKB0 | DRVCLKA0 |

|

|

|

|

|

|

|

|

|

|

0xA0A | Write | NU | NU | NU | NU | DRVCLKB1 | DRVCLKA1 | DRVCLKB0 | DRVCLKA0 |

|

|

|

|

|

|

|

|

|

|

| Reset | X | X | X | X | X | 0 | X | 0 |

|

|

|

|

|

|

|

|

|

|

PRI_LOS: Loss of primary reference clock detected: this bit is high when the primary clock at the input of the PLL (i.e., after PLD mux) is lost.

SEC_LOS: Loss of secondary reference clock detected: this bit is high when the primary clock at the input of the PLL (i.e. after PLD mux) is lost.

HOLDOVER: Holdover detected by the PLL

UNLOCK: Unlock detected by the PLL

DRVCLKA1: Drive transmission clock CLKA1 for AdvancedMC module B2: this bit is forced to 0 when advancedMC module B2 is absent or unpowered.

DRVCLKA0: Drive transmission clock CLKA0 for AdvancedMC module B1: this bit is forced to 0 when AdvancedMC module B1 is absent or unpowered.

DRVCLKB1: Drive transmission clock CLKB1 for AdvancedMC module B2. This bit is forced to 0 when AdvancedMC module B2 is absent or unpowered.

DRVCLKB0: Drive transmission clock CLKB0 for AdvancedMC module B1. This bit is forced to 0 when AdvancedMC module B1 is absent or unpowered.

Intel NetStructure® MPCBL0010 Single Board Computer |

|

Technical Product Specification | October 2006 |

172 | Order Number: 304120 |