MPCBL0010

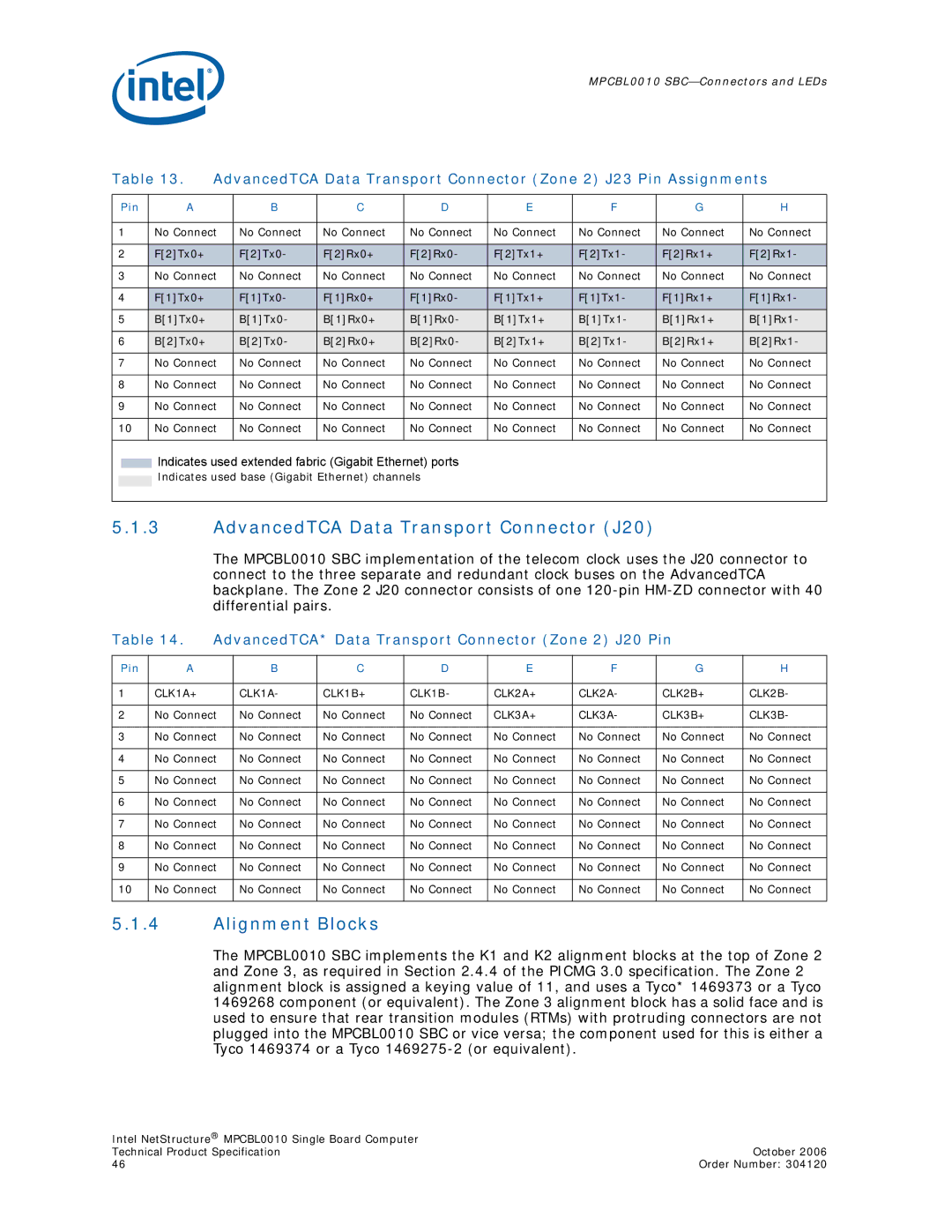

Table 13. | AdvancedTCA Data Transport Connector (Zone 2) J23 Pin Assignments | |||||||||

|

|

|

|

|

|

|

|

|

|

|

| Pin | A |

| B | C | D | E | F | G | H |

|

|

|

|

|

|

|

|

|

| |

1 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | ||

|

|

|

|

|

|

|

|

|

|

|

2 | F[2]Tx0+ |

| F[2]Tx0- | F[2]Rx0+ | F[2]Rx0- | F[2]Tx1+ | F[2]Tx1- | F[2]Rx1+ | F[2]Rx1- | |

|

|

|

|

|

|

|

|

|

| |

3 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | ||

|

|

|

|

|

|

|

|

|

|

|

4 | F[1]Tx0+ |

| F[1]Tx0- | F[1]Rx0+ | F[1]Rx0- | F[1]Tx1+ | F[1]Tx1- | F[1]Rx1+ | F[1]Rx1- | |

|

|

|

|

|

|

|

|

|

|

|

5 | B[1]Tx0+ |

| B[1]Tx0- | B[1]Rx0+ | B[1]Rx0- | B[1]Tx1+ | B[1]Tx1- | B[1]Rx1+ | B[1]Rx1- | |

|

|

|

|

|

|

|

|

|

|

|

6 | B[2]Tx0+ |

| B[2]Tx0- | B[2]Rx0+ | B[2]Rx0- | B[2]Tx1+ | B[2]Tx1- | B[2]Rx1+ | B[2]Rx1- | |

|

|

|

|

|

|

|

|

|

| |

7 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | ||

|

|

|

|

|

|

|

|

|

| |

8 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | ||

|

|

|

|

|

|

|

|

|

| |

9 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | ||

|

|

|

|

|

|

|

|

|

| |

10 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | ||

|

|

|

|

|

|

|

|

|

| |

|

| Indicates used extended fabric (Gigabit Ethernet) ports |

|

|

|

| ||||

|

|

|

|

|

| |||||

|

| Indicates used base (Gigabit Ethernet) channels |

|

|

|

| ||||

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

5.1.3AdvancedTCA Data Transport Connector (J20)

The MPCBL0010 SBC implementation of the telecom clock uses the J20 connector to connect to the three separate and redundant clock buses on the AdvancedTCA backplane. The Zone 2 J20 connector consists of one

Table 14. | AdvancedTCA* Data Transport Connector (Zone 2) J20 Pin |

| |||||||

|

|

|

|

|

|

|

|

|

|

Pin | A |

| B | C | D | E | F | G | H |

|

|

|

|

|

|

|

|

|

|

1 | CLK1A+ |

| CLK1A- | CLK1B+ | CLK1B- | CLK2A+ | CLK2A- | CLK2B+ | CLK2B- |

|

|

|

|

|

|

|

|

| |

2 | No Connect | No Connect | No Connect | No Connect | CLK3A+ | CLK3A- | CLK3B+ | CLK3B- | |

|

|

|

|

|

|

|

|

| |

3 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | |

|

|

|

|

|

|

|

|

| |

4 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | |

|

|

|

|

|

|

|

|

| |

5 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | |

|

|

|

|

|

|

|

|

| |

6 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | |

|

|

|

|

|

|

|

|

| |

7 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | |

|

|

|

|

|

|

|

|

| |

8 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | |

|

|

|

|

|

|

|

|

| |

9 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | |

|

|

|

|

|

|

|

|

| |

10 | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | No Connect | |

|

|

|

|

|

|

|

|

|

|

5.1.4Alignment Blocks

The MPCBL0010 SBC implements the K1 and K2 alignment blocks at the top of Zone 2 and Zone 3, as required in Section 2.4.4 of the PICMG 3.0 specification. The Zone 2 alignment block is assigned a keying value of 11, and uses a Tyco* 1469373 or a Tyco 1469268 component (or equivalent). The Zone 3 alignment block has a solid face and is used to ensure that rear transition modules (RTMs) with protruding connectors are not plugged into the MPCBL0010 SBC or vice versa; the component used for this is either a Tyco 1469374 or a Tyco

Intel NetStructure® MPCBL0010 Single Board Computer |

|

Technical Product Specification | October 2006 |

46 | Order Number: 304120 |