Error

8.0Error Messages

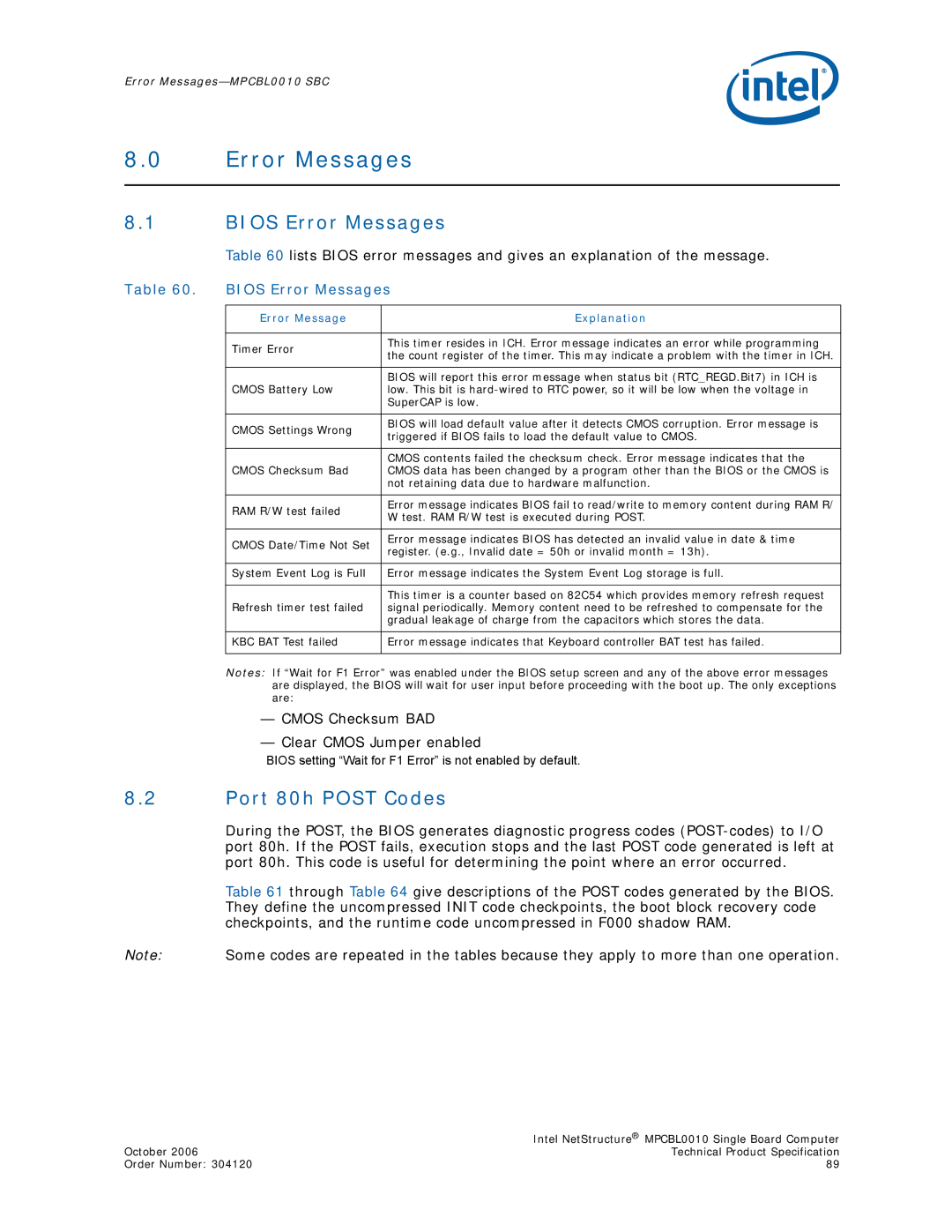

8.1BIOS Error Messages

| Table 60 lists BIOS error messages and gives an explanation of the message. | |

Table 60. | BIOS Error Messages | |

|

|

|

| Error Message | Explanation |

|

|

|

| Timer Error | This timer resides in ICH. Error message indicates an error while programming |

| the count register of the timer. This may indicate a problem with the timer in ICH. | |

|

| |

|

|

|

|

| BIOS will report this error message when status bit (RTC_REGD.Bit7) in ICH is |

| CMOS Battery Low | low. This bit is |

|

| SuperCAP is low. |

|

|

|

| CMOS Settings Wrong | BIOS will load default value after it detects CMOS corruption. Error message is |

| triggered if BIOS fails to load the default value to CMOS. | |

|

| |

|

|

|

|

| CMOS contents failed the checksum check. Error message indicates that the |

| CMOS Checksum Bad | CMOS data has been changed by a program other than the BIOS or the CMOS is |

|

| not retaining data due to hardware malfunction. |

|

|

|

| RAM R/W test failed | Error message indicates BIOS fail to read/write to memory content during RAM R/ |

| W test. RAM R/W test is executed during POST. | |

|

| |

|

|

|

| CMOS Date/Time Not Set | Error message indicates BIOS has detected an invalid value in date & time |

| register. (e.g., Invalid date = 50h or invalid month = 13h). | |

|

| |

|

|

|

| System Event Log is Full | Error message indicates the System Event Log storage is full. |

|

|

|

|

| This timer is a counter based on 82C54 which provides memory refresh request |

| Refresh timer test failed | signal periodically. Memory content need to be refreshed to compensate for the |

|

| gradual leakage of charge from the capacitors which stores the data. |

|

|

|

| KBC BAT Test failed | Error message indicates that Keyboard controller BAT test has failed. |

|

|

|

Notes: If “Wait for F1 Error” was enabled under the BIOS setup screen and any of the above error messages are displayed, the BIOS will wait for user input before proceeding with the boot up. The only exceptions are:

—CMOS Checksum BAD

—Clear CMOS Jumper enabled

BIOS setting “Wait for F1 Error” is not enabled by default.

8.2Port 80h POST Codes

During the POST, the BIOS generates diagnostic progress codes

Table 61 through Table 64 give descriptions of the POST codes generated by the BIOS. They define the uncompressed INIT code checkpoints, the boot block recovery code checkpoints, and the runtime code uncompressed in F000 shadow RAM.

Note: Some codes are repeated in the tables because they apply to more than one operation.

| Intel NetStructure® MPCBL0010 Single Board Computer |

October 2006 | Technical Product Specification |

Order Number: 304120 | 89 |