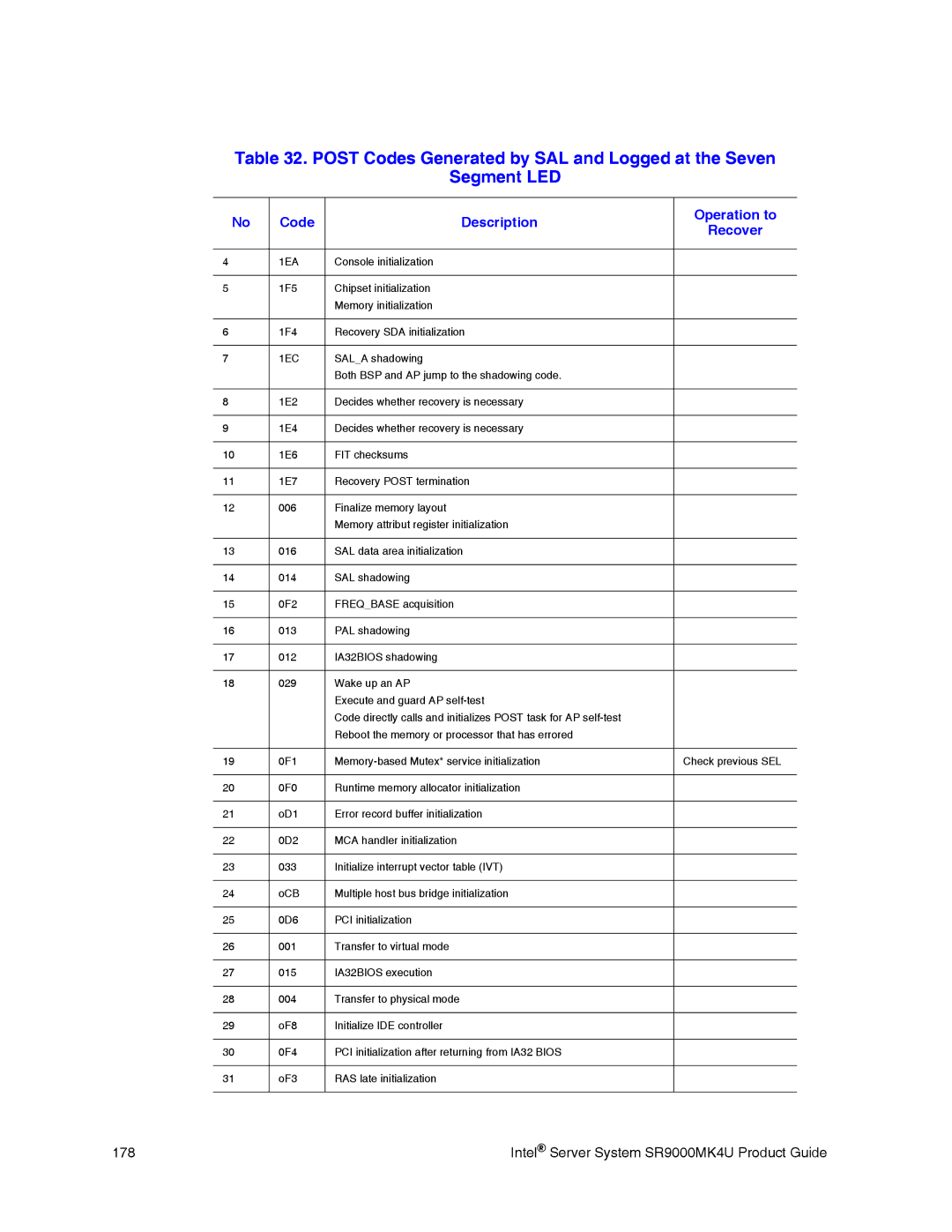

Table 32. POST Codes Generated by SAL and Logged at the Seven

Segment LED

No | Code | Description | Operation to | |

Recover | ||||

|

|

| ||

|

|

|

| |

4 | 1EA | Console initialization |

| |

|

|

|

| |

5 | 1F5 | Chipset initialization |

| |

|

| Memory initialization |

| |

|

|

|

| |

6 | 1F4 | Recovery SDA initialization |

| |

|

|

|

| |

7 | 1EC | SAL_A shadowing |

| |

|

| Both BSP and AP jump to the shadowing code. |

| |

|

|

|

| |

8 | 1E2 | Decides whether recovery is necessary |

| |

|

|

|

| |

9 | 1E4 | Decides whether recovery is necessary |

| |

|

|

|

| |

10 | 1E6 | FIT checksums |

| |

|

|

|

| |

11 | 1E7 | Recovery POST termination |

| |

|

|

|

| |

12 | 006 | Finalize memory layout |

| |

|

| Memory attribut register initialization |

| |

|

|

|

| |

13 | 016 | SAL data area initialization |

| |

|

|

|

| |

14 | 014 | SAL shadowing |

| |

|

|

|

| |

15 | 0F2 | FREQ_BASE acquisition |

| |

|

|

|

| |

16 | 013 | PAL shadowing |

| |

|

|

|

| |

17 | 012 | IA32BIOS shadowing |

| |

|

|

|

| |

18 | 029 | Wake up an AP |

| |

|

| Execute and guard AP |

| |

|

| Code directly calls and initializes POST task for AP |

| |

|

| Reboot the memory or processor that has errored |

| |

|

|

|

| |

19 | 0F1 | Check previous SEL | ||

|

|

|

| |

20 | 0F0 | Runtime memory allocator initialization |

| |

|

|

|

| |

21 | oD1 | Error record buffer initialization |

| |

|

|

|

| |

22 | 0D2 | MCA handler initialization |

| |

|

|

|

| |

23 | 033 | Initialize interrupt vector table (IVT) |

| |

|

|

|

| |

24 | oCB | Multiple host bus bridge initialization |

| |

|

|

|

| |

25 | 0D6 | PCI initialization |

| |

|

|

|

| |

26 | 001 | Transfer to virtual mode |

| |

|

|

|

| |

27 | 015 | IA32BIOS execution |

| |

|

|

|

| |

28 | 004 | Transfer to physical mode |

| |

|

|

|

| |

29 | oF8 | Initialize IDE controller |

| |

|

|

|

| |

30 | 0F4 | PCI initialization after returning from IA32 BIOS |

| |

|

|

|

| |

31 | oF3 | RAS late initialization |

| |

|

|

|

|

178 | Intel® Server System SR9000MK4U Product Guide |