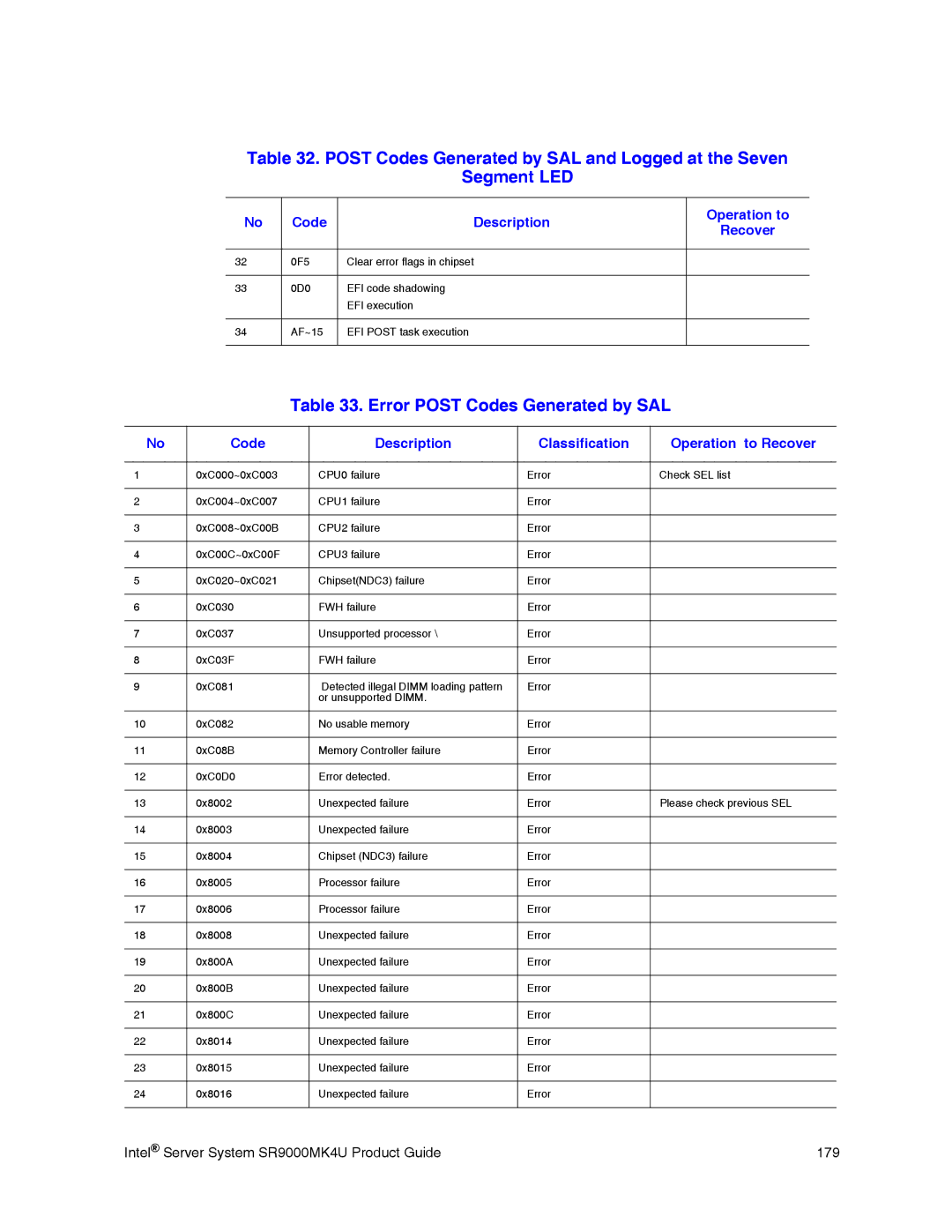

Table 32. POST Codes Generated by SAL and Logged at the Seven

Segment LED

No | Code | Description | Operation to | |

Recover | ||||

|

|

| ||

|

|

|

| |

32 | 0F5 | Clear error flags in chipset |

| |

|

|

|

| |

33 | 0D0 | EFI code shadowing |

| |

|

| EFI execution |

| |

|

|

|

| |

34 | AF~15 | EFI POST task execution |

| |

|

|

|

|

Table 33. Error POST Codes Generated by SAL

No | Code | Description | Classification | Operation to Recover |

|

|

|

|

|

1 | 0xC000~0xC003 | CPU0 failure | Error | Check SEL list |

|

|

|

|

|

2 | 0xC004~0xC007 | CPU1 failure | Error |

|

|

|

|

|

|

3 | 0xC008~0xC00B | CPU2 failure | Error |

|

|

|

|

|

|

4 | 0xC00C~0xC00F | CPU3 failure | Error |

|

|

|

|

|

|

5 | 0xC020~0xC021 | Chipset(NDC3) failure | Error |

|

|

|

|

|

|

6 | 0xC030 | FWH failure | Error |

|

|

|

|

|

|

7 | 0xC037 | Unsupported processor \ | Error |

|

|

|

|

|

|

8 | 0xC03F | FWH failure | Error |

|

|

|

|

|

|

9 | 0xC081 | Detected illegal DIMM loading pattern | Error |

|

|

| or unsupported DIMM. |

|

|

|

|

|

|

|

10 | 0xC082 | No usable memory | Error |

|

|

|

|

|

|

11 | 0xC08B | Memory Controller failure | Error |

|

|

|

|

|

|

12 | 0xC0D0 | Error detected. | Error |

|

|

|

|

|

|

13 | 0x8002 | Unexpected failure | Error | Please check previous SEL |

|

|

|

|

|

14 | 0x8003 | Unexpected failure | Error |

|

|

|

|

|

|

15 | 0x8004 | Chipset (NDC3) failure | Error |

|

|

|

|

|

|

16 | 0x8005 | Processor failure | Error |

|

|

|

|

|

|

17 | 0x8006 | Processor failure | Error |

|

|

|

|

|

|

18 | 0x8008 | Unexpected failure | Error |

|

|

|

|

|

|

19 | 0x800A | Unexpected failure | Error |

|

|

|

|

|

|

20 | 0x800B | Unexpected failure | Error |

|

|

|

|

|

|

21 | 0x800C | Unexpected failure | Error |

|

|

|

|

|

|

22 | 0x8014 | Unexpected failure | Error |

|

|

|

|

|

|

23 | 0x8015 | Unexpected failure | Error |

|

|

|

|

|

|

24 | 0x8016 | Unexpected failure | Error |

|

|

|

|

|

|

Intel® Server System SR9000MK4U Product Guide | 179 |