| INTERRUPTS AND EXCEPTIONS |

|

|

|

| |

| Table |

|

|

| ||

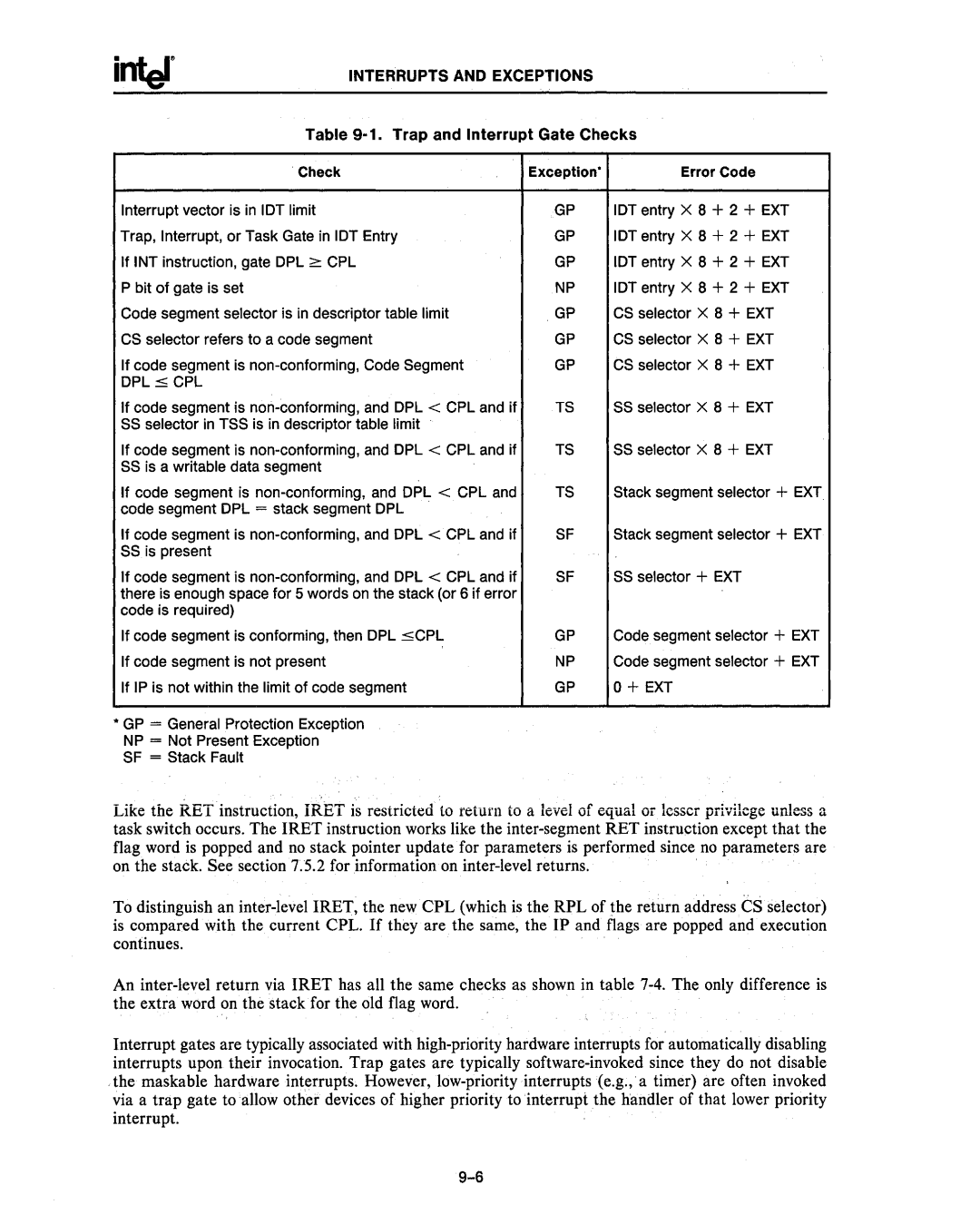

Check | Exception' | Error Code |

|

| ||

Interrupt vector is in lOT limit | GP | lOT entry X 8 + 2 + | EXT |

| ||

Trap, Interrupt, or Task Gate in lOT Entry | GP | IDTentry X 8 + 2 + | EXT |

| ||

If INT instruction, gate OPL ~ CPL | GP | lOT entry X 8 + 2 + | EXT |

| ||

P bit of gate is set |

| NP | lOT entry X 8 + 2 + | EXT |

| |

Code segment selector is in descriptor table limit | GP | CS selector X 8 + | EXT |

| ||

CS selector refers to a code segment | GP | CS selector X 8 + | EXT |

| ||

If code segment is | GP | CS selector X 8 + | EXT |

| ||

OPL =:; CPL |

|

|

|

|

|

|

If code segment is | T8 | 88 selector X 8 + | EXT |

| ||

SS selector in TSS is in descriptor table limit |

|

|

|

|

| |

If code segment is | TS | SS selector X 8 + | EXT |

| ||

SS is a writable data segment |

|

|

|

|

| |

If code segment is | TS | Stack segment selector + | EXT | |||

code segment OPL = stack segment OPL |

|

|

|

|

| |

If code segment is | SF | Stack segment selector + | EXT | |||

SS is present |

|

|

|

|

|

|

If code segment is | SF | SS selector + EXT |

|

|

| |

there is enough space for 5 words on the stack (or 6 if error |

|

|

|

|

| |

code is required) |

|

|

|

|

|

|

If code segment is conforming, then OPL =:;CPL | GP | Code segment selector + EXT | ||||

If code segment is not present | NP | Code segment selector + | EXT | |||

If IP is not within the limit of code segment | GP | 0+ EXT |

|

|

| |

• GP = General Protection Exception |

|

|

|

|

| |

NP = Not Present Exception |

|

|

|

|

| |

SF = Stack Fault |

|

|

|

|

|

|

, | ' ',' . |

|

|

|

|

|

Like the RET instruction, | ntET is restricted to return to a level of equal or lesscr privilege unless a | |||||

task switch occurs. The IRET instruction works like the

on the stack. See section 7:5.2 for information on

To distinguish an

continues. | ' |

An

Interrupt gates are typically associated with