INTERRUPTS AND EXCEPTIONS

+7 |

|

|

| INTEL RESERVED' |

| +6 |

+5 | PIDP21 0 | 10 | 1 | 1 | UNUSED | +4 |

|

| T I |

|

| ||

+3 | INTERRUPT CODE SEGMENT SELECTOR | +2 | ||||

+1 |

| INTERRUPT CODE OFFSET |

| |||

T = 1 FOR TRAP GATE

'MUST BE SET TO 0 FOR

COMPATIBILITY WITH THE 80386 T = 0 FOR INTERRUPT GI\TE

G30108

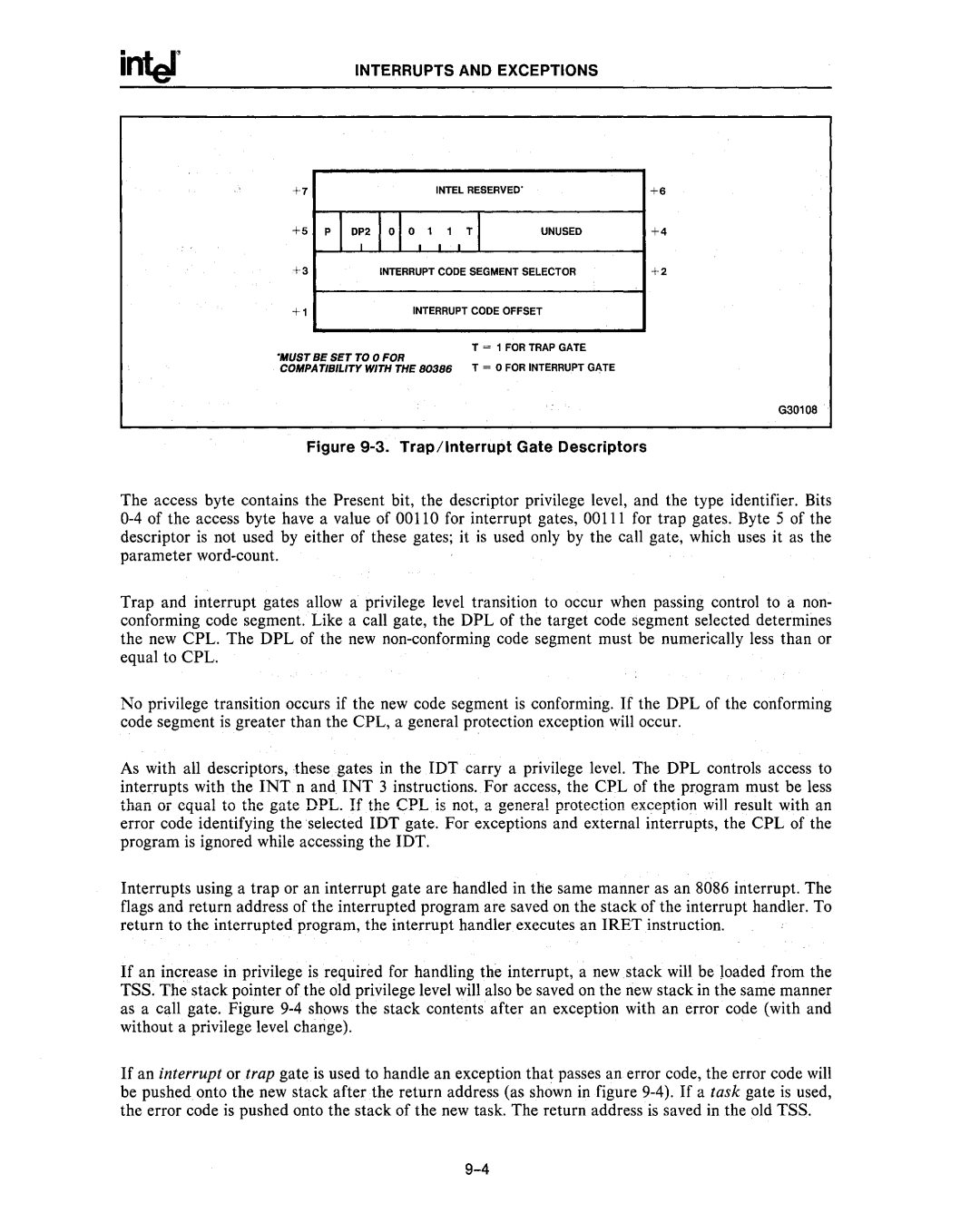

Figure 9-3. Trap/Interrupt Gate Descriptors

The access byte contains the Present bit, the descriptor privilege level, and the type identifier. Bits

Trap and interrupt gates allow a' privilege level transition to occur when passing control to a non- conforming code segment. Like a call gate, the DPL of the target code segment selected determines the new CPL. The DPL of the new

No privilege transition occurs if the new code segment is conforming. If the DPL of the conforming code segment is greater than the CPL, a general protection exception will occur.

As with all descriptors, these ,gates in the IDT carry a privilege level. The DPL controls access to interrupts with the INT nand INT 3 instructions. For access, the CPL of the program must be less than Oi equal to the gate DPL. If tile CPL is not, a general protection exception will result with an error code identifying the selected IDT gate. For exceptions and external interrupts, the CPL of the program is ignored while accessing the IDT.

Interrupts using a trap or an interrupt gate are handled in the same manner as an 8086 interrupt. The flags and return address of the interrupted program are saved on the stack of the interrupt handler. To return to the interrupted program, the interrupt handler executes an IRET instruction.

If an increase in privilege is required for handling the interrupt, a new stack will be Joaded from the TSS. The stack pointer of the old privilege level will also be saved on the new stack in the same manner as a call gate. Figure

If an interrupt or trap gate is used to handle an exception that passes an error code, the error code will be pushed onto the new stack after the return address (as shown in figure