| |

| Table |

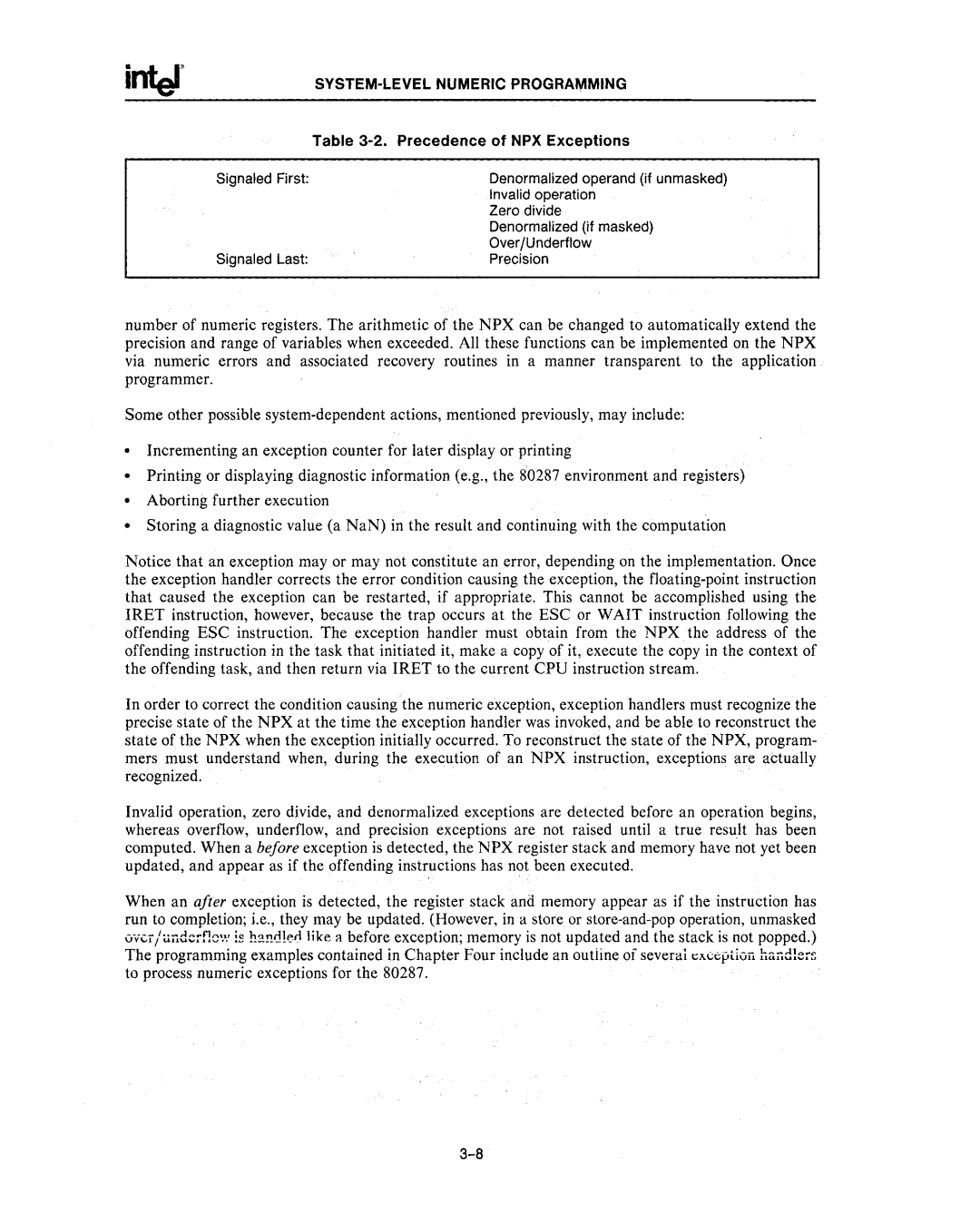

Signaled First: | Denormalized operand (if unmasked) |

| Invalid operation |

| Zero divide |

| Denormalized (if masked) |

Signaled Last: | Over/U nderflow |

Precision |

number of numeric registers. The arithmetic of the NPX can be changed to automatically extend the precision and range of variables when exceeded. All these functions can be implemented on the NPX via numeric errors and associated recovery routines in a manner transparent to the application programmer.

Some other possible

Incrementing an exception counter for later display or printing

Printing or displaying diagnostic information (e.g., the 80287 environment and registers)

•Aborting further execution

Storing a diagnostic value (a NaN) in the result and continuing with the computation

Notice that an exception mayor may not constitute an error, depending on the implementation. Once the exception handler corrects the error condition causing the exception, the

In order to correct the condition causing the numeric exception, exception handlers must recognize the precise state of the NPX at the time the exception handler was invoked, and be able to reconstruct the state of the NPX when the exception initially occurred. To reconstruct the state of the NPX, program- mers must understand when, during the execution of an NPX instruction, exceptions are actually

recognized. | . |

Invalid operation, zero divide, and denormalized exceptions are detected before an operation begins, whereas overflow, underflow, and precision exceptions are not raised until a true result has been computed. When a before exception is detected, the NPX register stack and memory have ilOt yet been updated, and appear as if the offending instructions has not been executed.

When an after exception is detected, the register stack and memory appear as if the instruction has run to completion; i.e., they may be updated. (However, in a store or