SYSTEM CONTROL AND INITIALIZATION

7 | 07 |

| o |

+5 | INTEL RESERVED' I | BASE23·'6 | +4 |

+3 | BAS~'5.0 |

| +2 |

+1 | LIMIT,5'O |

| o |

15 | B 7 |

| o |

'MUST BE SET TO 0 FOR

COMPA TlBIL/TY WITH THE 80386

G30108

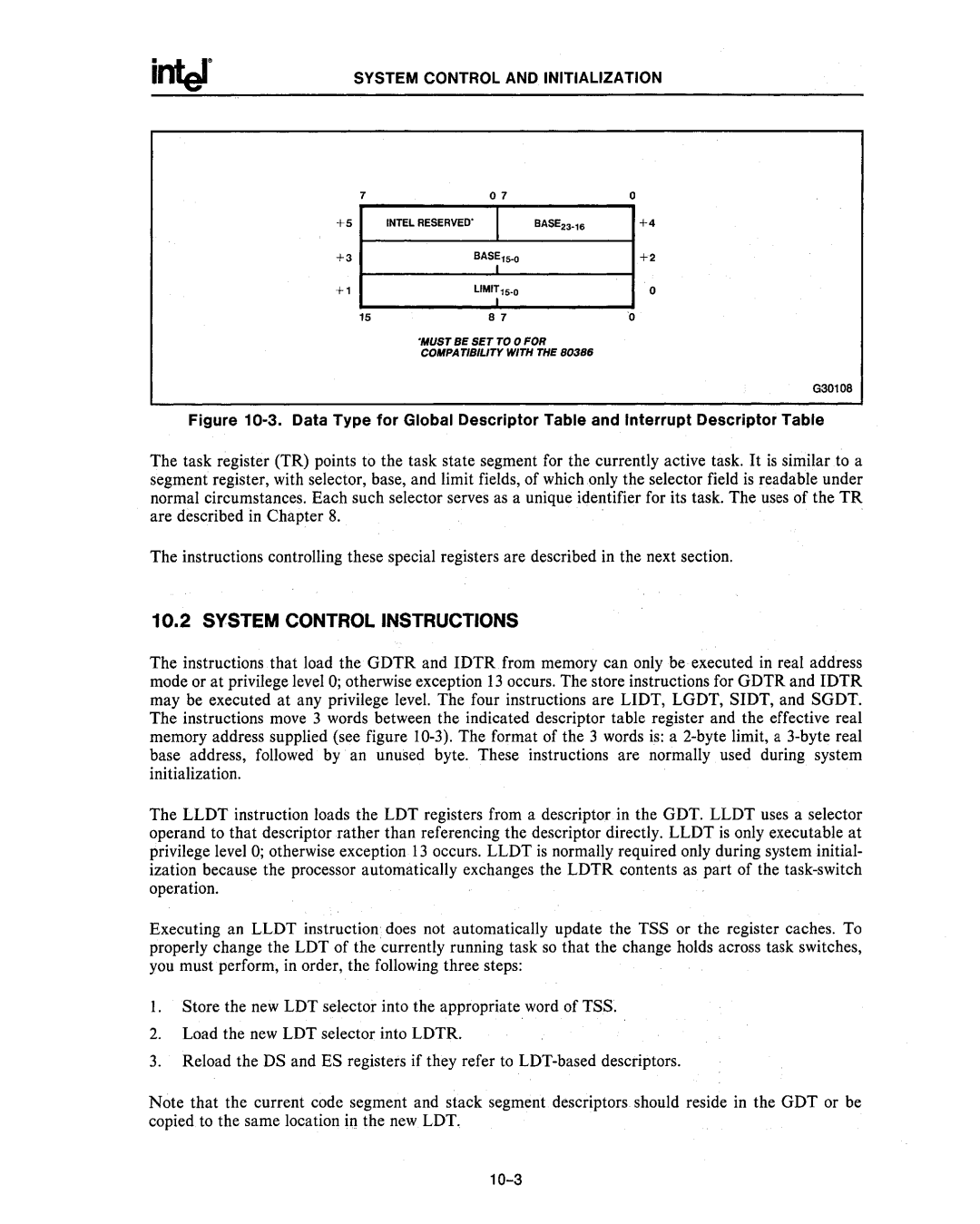

Figure 10-3. Data Type for Global Descriptor Table and Interrupt Descriptor Table

The task register (TR) points to the task state segment for the currently active task. It is similar to a segment register, with selector, base, and limit fields, of which.only the selector field is readable under normal circumstances. Each such selector serves as a unique identifier for its task. The uses of the TR are described In Chapter 8.

The instructions controlling these special registers are described in the next section.

10.2SYSTEM CONTROL INSTRUCTIONS

The instructions that load the GDTR and IDTR from memory can only be executed in real address mode or at privilege level 0; otherwise exception 13 occurs. The store instructions for GDTR and IDTR may be executed at any privilege level. The four instructions are LIDT, LGDT, SIDT, and SGDT. The instructions move 3 words between the indicated descriptor table register and the effective real memory address supplied (see figure

The LLDT instruction loads the LDT registers from a descriptor in the GDT. LLDT uses a selector operand to that descriptor rather than referencing the descriptor directly. LLDT is only executable at privilege level 0; otherwise exception 13 occurs. LLDT is normally required only during system initial- ization because the processor automatically exchanges the LDTR contents as part of the

Executing an LLDT instruction'does not automatically update the TSS or the register caches. To properly change the LDT of the currently running task so that the change holds across task switches, you must perform, in order, the following three steps:

1.Store the new LDT selector into the appropriate word of TSS.

2.Load the new LDT selector into LDTR.

3.Reload the DS and ES registers if they refer to

Note that the current code segment and stack segment descriptors. should reside in the GDT or be copied to the same location in the new LDT.