THE. 80286 INSTRUCTION SET

LAR-Load Access Rights Byte

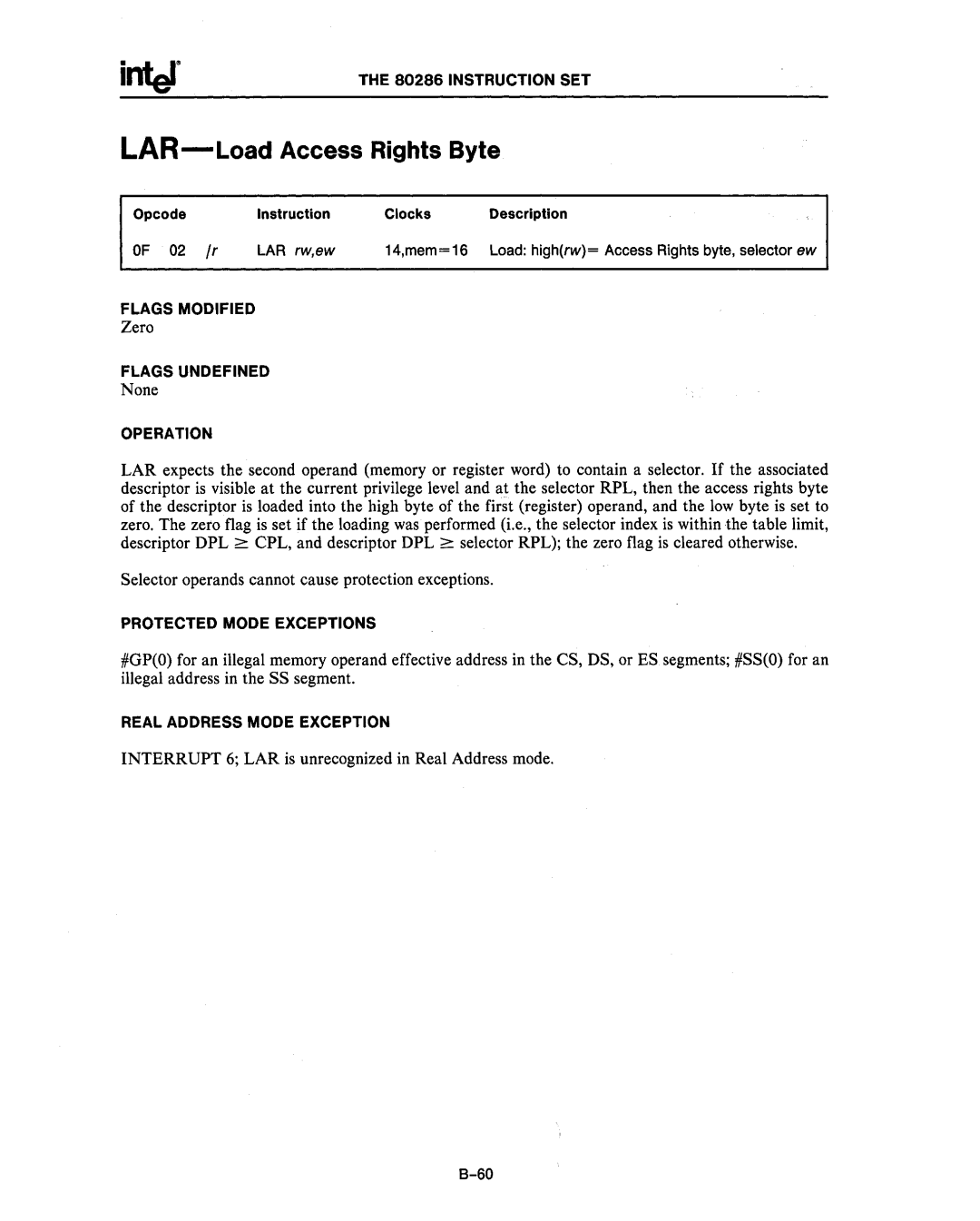

OpcodeInstruction Clocks Description

OF 02 Ir | LAR rW,ew | 14,mem=16 Load: high(rw)= Access Rights byte, selector ew |

FLAGS MODIFIED

Zero

FLAGS UNDEFINED

None

OPERATION

LAR expects the second operand (memory or register word) to contain a selector. If the associated descriptor is visible at the current privilege level and at the selector RPL, then the access rights byte of the descriptor is loaded into the high byte of the first (register) operand, and the low byte is set to zero. The zero flag is set if the loading was performed (i.e., the selector index is within the table limit, descriptor DPL :2: CPL, and descriptor DPL :2: selector RPL); the zero flag is cleared otherwise.

Selector operands cannot cause protection exceptions.

PROTECTED MODE EXCEPTIONS

#GP(O) for an illegal memory operand effective address in the CS, DS, or ES segments; #SS(O) for an illegal address in the SS segment.

REAL ADDRESS MODE EXCEPTION

INTERRUPT 6; LAR is unrecognized in Real Address mode.