PROGRAMMING NUMERIC APPLICATIONS

FABS

FABS (absolute value) changes the top stack element to its absolute value by making its sign positive.

FCHS

FCHS (change sign) complements (reverses) the sign of the top stack element.

Comparison Instructions

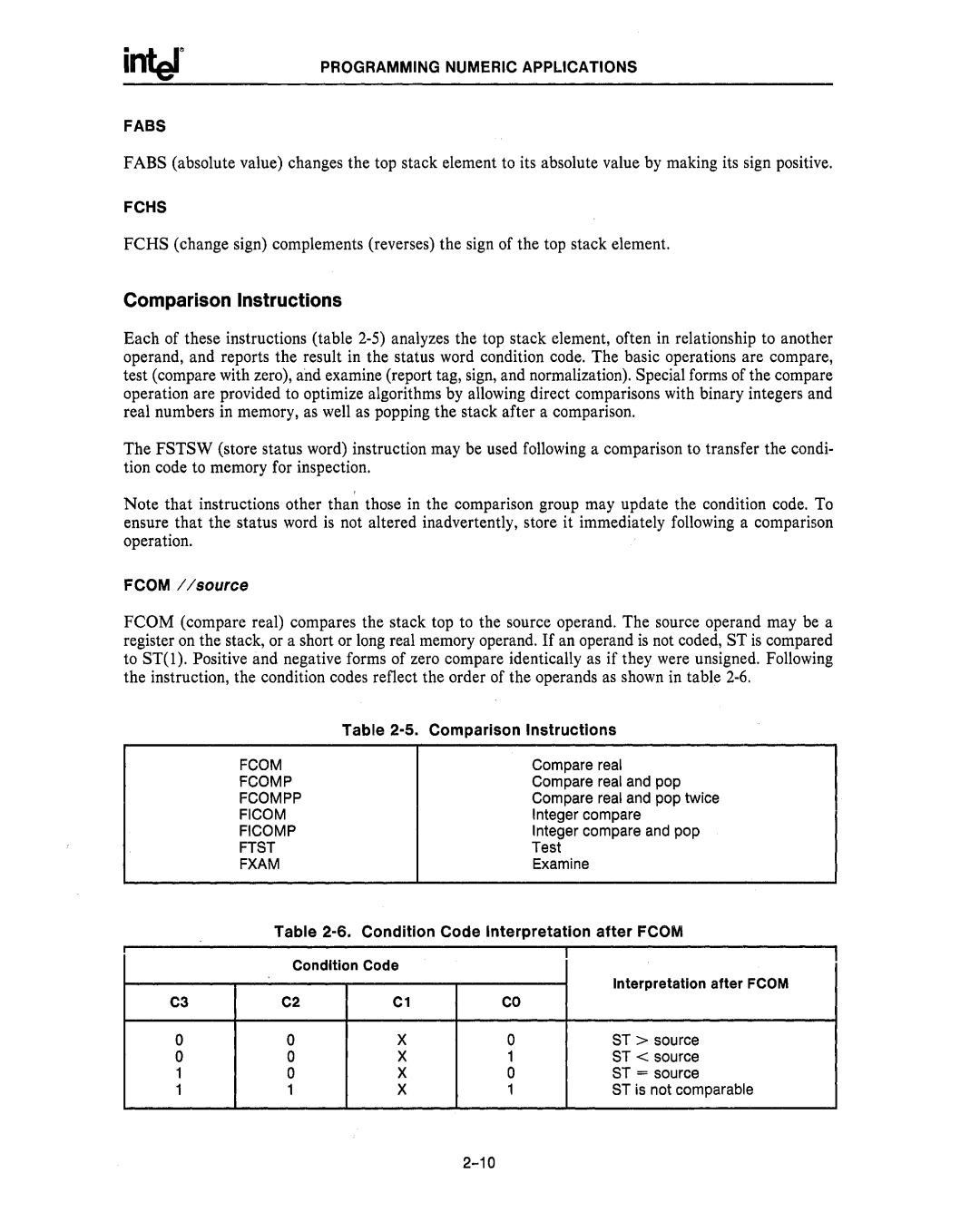

Each of these instructions (table

The FSTSW (store status word) instruction may be used following a comparison to transfer the condi- tion code to memory for inspection.

Note that instructions other than those in the comparison group may update the condition code. To ensure that the status word is not altered inadvertently, store it immediately following a comparison operation.

FCOM / /source

FCOM (compare real) compares the stack top to the source operand. The source operand may be a register on the stack, or a short or long real memory operand. If an operand is not coded, ST is compared to ST(1). Positive and negative forms of zero compare identically as if they were unsigned. Following the instruction, the condition codes reflect the order of the operands as shown in table

|

| Table | ||

| FCOM |

|

| Compare real |

| FCOMP |

|

| Compare real and pop |

| FCOMPP |

|

| Compare real and pop twice |

| FICOM |

|

| Integer compare |

| FICOMP |

|

| Integer compare and pop |

| FTST |

|

| Test |

| FXAM |

|

| Examine |

| Table | |||

| Condition Code |

|

| |

|

|

|

| Interpretation after FCOM |

C3 | C2 | C1 | CO |

|

0 | 0 | X | 0 | ST> source |

0 | 0 | X | 1 | ST < source |

1 | 0 | X | 0 | ST = source |

1 | 1 | X | 1 | ST is not comparable |