TASKS AND STATE TRANSITIONS

The linking order of tasks may need to be changed to restart an interrupted task before the task that interrupted it completes. To remove a task from the list, trusted operating system software must change the backlink field in the TSS of the interrupting task first, then clear the busy bit in the TSS descriptor of the task removed from the list.

When trusted software deletes the link from one task to another, it should place a value in the backlink field, which will pass control to that trusted software when the task attempts to resume execution of another task via IRET.

8.5TASK GATES

A task may be invoked by several different events. Task gates are provided to support this need. Task gates are used in the same way as call and interrupt gates. The ultimate effect of jumping to or calling a task gate is the same as jumping to or calling directly to the TSS in the task gate.

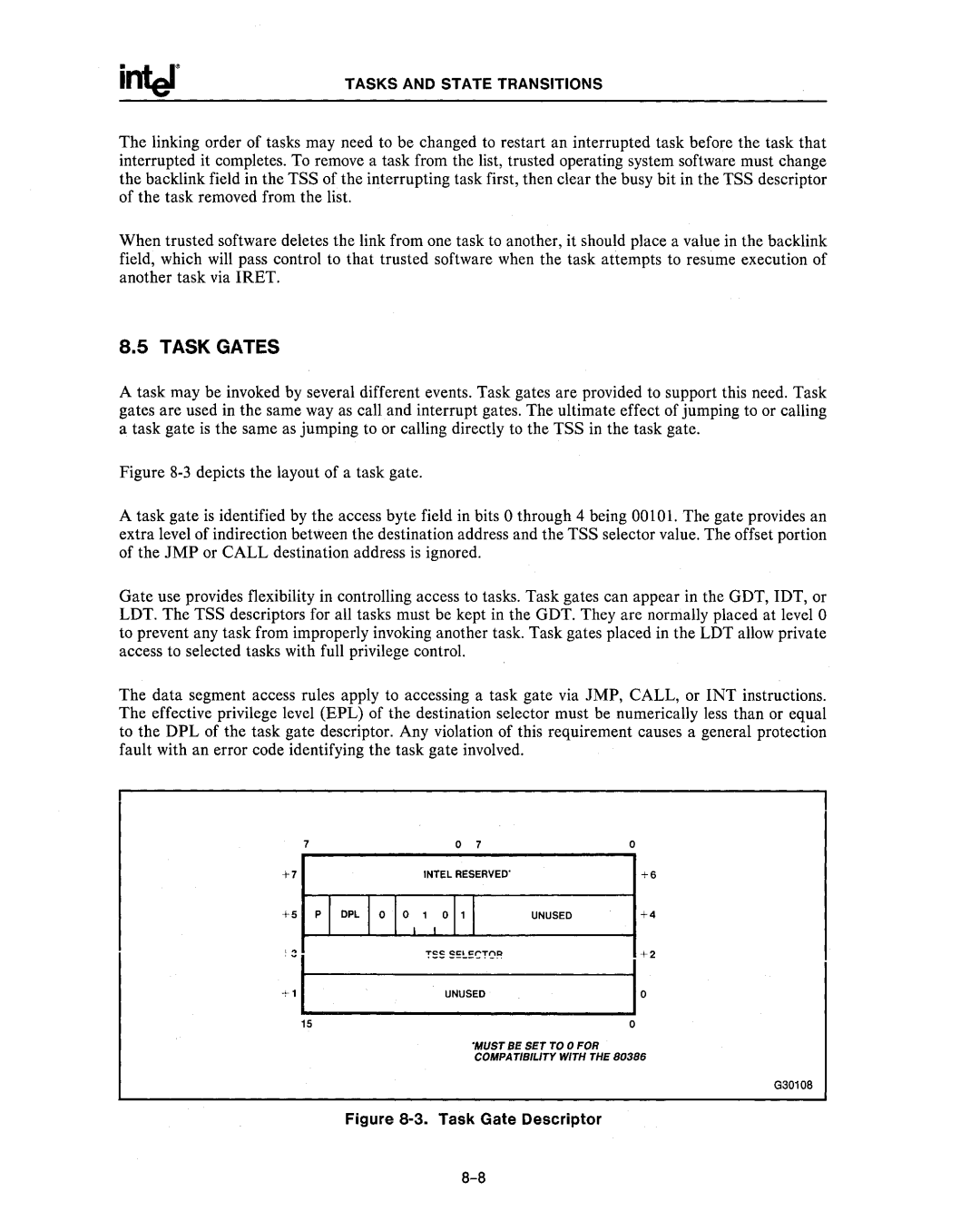

Figure 8-3 depicts the layout of a task gate.

A task gate is identified by the access byte field in bits 0 through 4 being 00101. The gate provides an extra level of indirection between the destination address and theTSS selector value. The offset portion of the JMP or CALL destination address is ignored.

Gate use provides flexibility in controlling access to tasks. Task gates can appear in the GDT, IDT, or LDT. The TSS descriptors for all tasks must be kept in the GDT. They are normally placed at level 0 to prevent any task from improperly invoking another task. Task gates placed in the LDT allow private access to selected tasks with full privilege control.

The data segment access rules apply to accessing a task gate via JMP, CALL, or INT instructions. The effective privilege level (EPL) of the destination selector must be numerically less than or equal to the DPL of the task gate descriptor. Any violation of this requirement causes a general protection fault with an error code identifying the task gate involved.

| 0 7 |

| 0 |

+7 | INTEL RESERVED· |

| +6 |

+5 | PIDPLlolo 1 01 1 1 | UNUSED | +4 |

| :~5 5=!,,=CT0~ |

| +2 |

,:1 UNUSED

15

10

0

·MUST BE SET TO 0 FOR COMPATIBILITY WITH THE 80386

G30108