MACHINE INSTRUCTION ENCODING AND DECODING

P:0 = do not pop stack

1 = pop stack after operation

REG: register stack element 000 = stack top

001 = next on stack

010 = third stack element, etc.

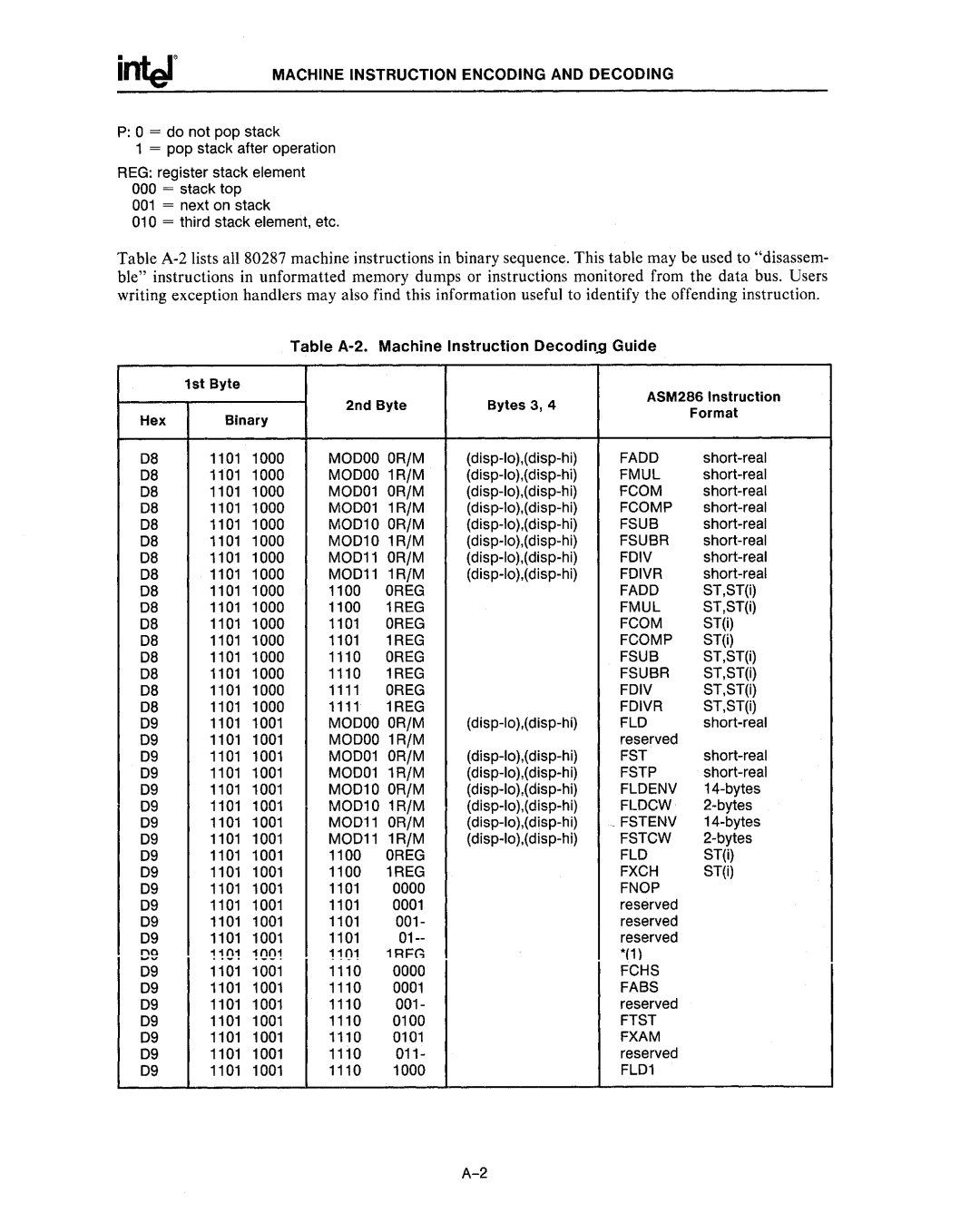

Table

Table A·2. Machine Instruction Decodin.9 Guide

| 1st Byte |

|

|

|

Hex | Binary | 2nd Byte | ||

|

| |||

08 | 1101 | 1000 | MOOOO OR/M | |

08 | 1101 | 1000 | MOOOO 1R/M | |

08 | 1101 | 1000 | M0001 | OR/M |

08 | 1101 | 1000 | M0001 | 1R/M |

08 | 1101 | 1000 | M0010 OR/M | |

08 | 1101 | 1000 | M0010 1R/M | |

08 | 1101 | 1000 | M0011 | OR/M |

08 | 1101 | 1000 | M0011 | 1R/M |

08 | 1101 | 1000 | 1100 | OREG |

08 | 1101 | 1000 | 1100 | 1REG |

08 | 1101 | 1000 | 1101 | OREG |

08 | 1101 | 1000 | 1101 | 1REG |

08 | 1101 | 1000 | 1110 | OREG |

08 | 1101 | 1000 | 1110 | 1REG |

08 | 1101 | 1000 | 1111 | OREG |

08 | 1101 | 1000 | 1111 | 1REG |

09 | 1101 | 1001 | MOOOO OR/M | |

09 | 1101 | 1001 | MOOOO 1R/M | |

09 | 1101 | 1001 | M0001 | OR/M |

09 | 1101 | 1001 | M0001 | 1R/M |

09 | 1101 | 1001 | M0010 OR/M | |

09 | 1101 | 1001 | M0010 1R/M | |

09 | 1101 | 1001 | M0011 | OR/M |

09 | 1101 | 1001 | M0011 | 1R/M |

09 | 1101 | 1001 | 1100 | OREG |

09 | 1101 | 1001 | 1100 | 1REG |

09 | 1101 | 1001 | 1101 | 0000 |

09 | 1101 | 1001 | 1101 | 0001 |

09 | 1101 | 1001 | 1101 | 001- |

09 | 1101 | 1001 | 1101 | |

D9 | 1101 | 1001 | 1101 | 1RFG |

09 | 1101 | 1001 | 1110 | 0000 |

09 | 1101 | 1001 | 1110 | 0001 |

09 | 1101 | 1001 | 1110 | 001· |

09 | 1101 | 1001 | 1110 | 0100 |

09 | 1101 | 1001 | 1110 | 0101 |

09 | 1101 | 1001 | 1110 | 011· |

09 | 1101 | 1001 | 1110 | 1000 |

Bytes 3,4 | ASM286 Instruction | |

| Format | |

|

| |

FAOO | ||

FMUL | ||

FCOM | ||

FCOMP | ||

FSUB | ||

FSUBR | ||

FOIV | ||

FOIVR | ||

| FAOO | ST,ST(i) |

| FMUL | ST,ST(i) |

| FCOM | ST(i) |

| FCOMP | ST(i) |

| FSUB | ST,ST(i) |

| FSUBR | ST,ST(i) |

| FOIV | ST,ST(i) |

| FOIVR | ST,ST(i) |

FLO | ||

| reserved |

|

FST | ||

FSTP | ||

FLOENV | ||

FLOCW | ||

~ FSTENV | ||

FSTCW | ||

| FLO | ST(i) |

| FXCH | ST(i) |

| FNOP |

|

reserved reserved reserved *(1 )

FCHS

FABS reserved

FTST

FXAM reserved FL01