OVERVIEW OF NUMERIC PROCESSING

| 79 | 78 |

| 80287 STACK: |

| TAG FIELD | |

| 64 | 63 | 0 | 1 | 0 | ||

Rl | SIGN |

| EXPONENT | SIGNIFICAND |

|

|

|

R2 |

|

|

|

|

|

|

|

R3 |

|

|

|

|

| r |

|

R5 |

|

|

|

|

|

| |

|

|

|

|

| - |

| |

R4 |

|

|

|

|

|

|

|

R6 |

|

|

|

|

|

|

|

R7 |

|

|

|

|

|

|

|

R8 |

|

|

|

|

|

|

|

|

|

| 15 |

| 0 |

|

|

|

|

|

| CONTROL REGISTER |

|

|

|

|

|

|

| STATUS REGISTER |

|

|

|

|

|

|

| TAG WORD |

|

|

|

|

|

| t- | INSTRUCTION POINTER |

|

|

|

|

|

|

| DATA POINTER |

|

|

|

G3010B

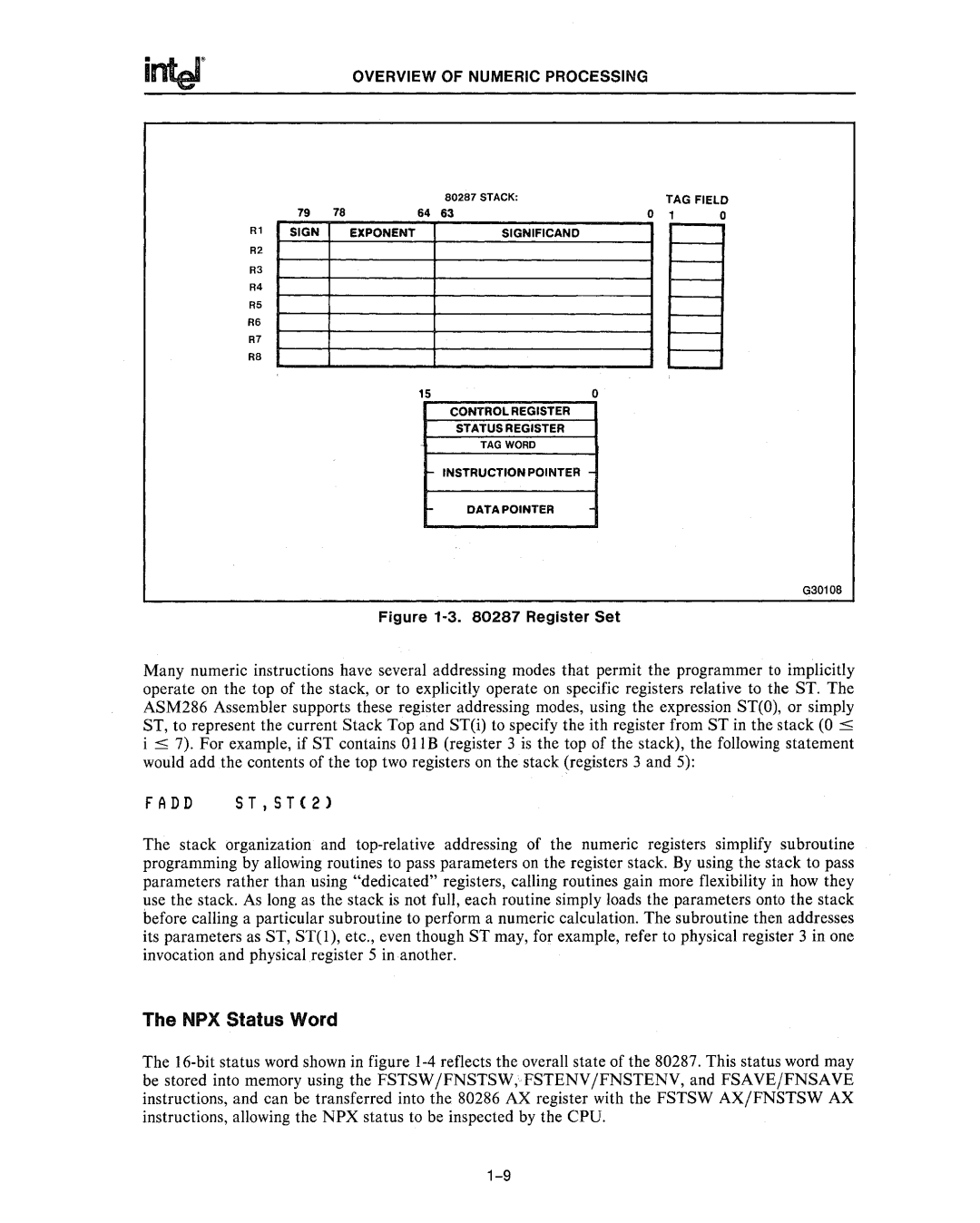

Figure 1-3_ 80287 Register Set

Many numeric instructions have several addressing modes that permit the programmer to implicitly operate on the top of the stack, or to explicitly operate on specific registers relative to the ST. The ASM286 Assembler supports these register addressing modes, using the expression ST(O), or simply ST, to represent the current Stack Top and STeil to specify the ith register from ST in the stack (0 ::s i ::s 7). For example, if ST contains OllB (register 3 is the top of the stack), the following statement would add the contents of the top two registers on the stack (registers 3 and 5):

FADD ST,ST(2)

The stack organization and

The NPX Status Word

The