MEMORY MANAGEMENT AND VIRTUAL ADDRESSING

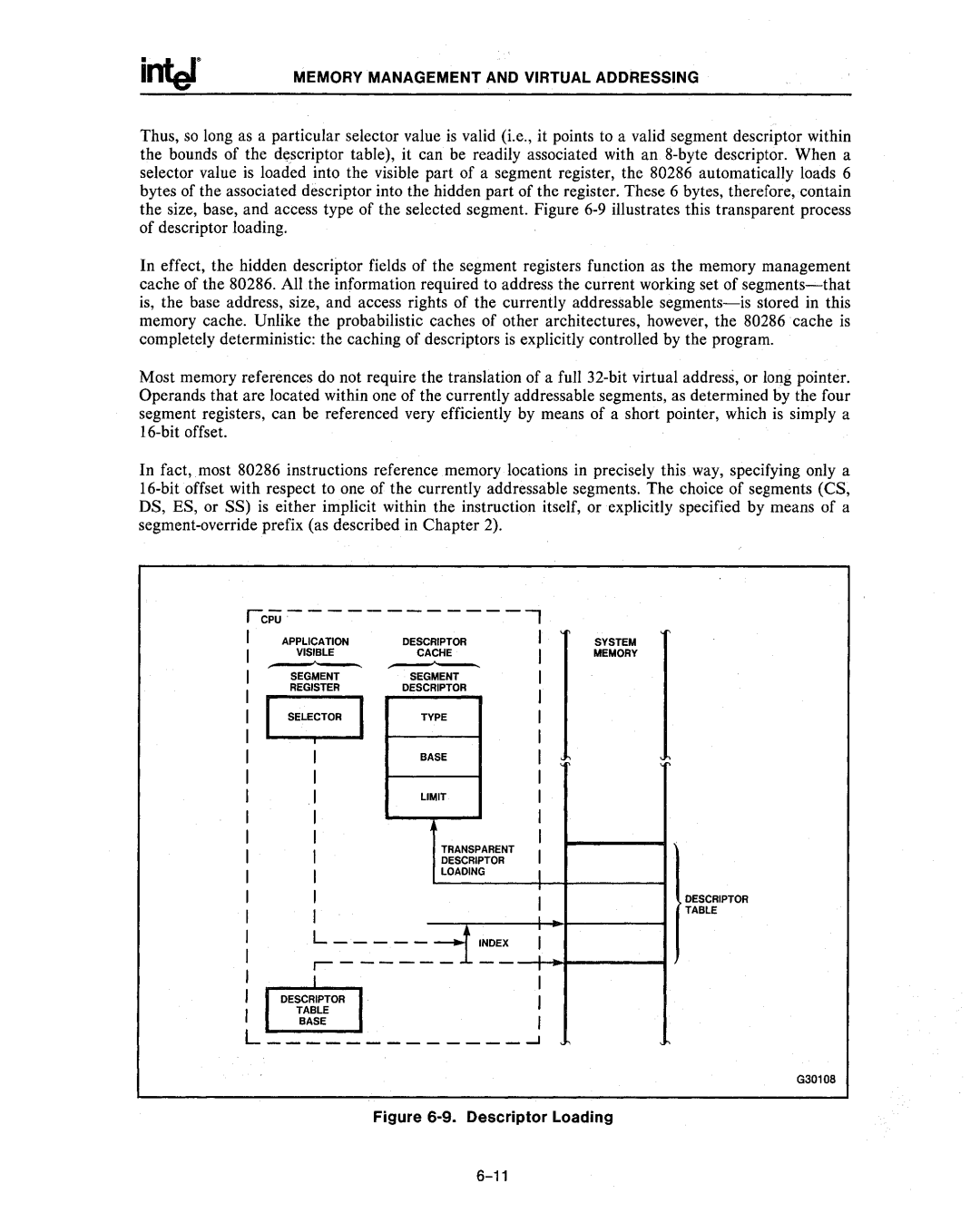

Thus, so long as a particular selector value is valid (i.e., it points to a valid segment descriptor within the bounds of the d()scriptor table), it can be readily associated with an

In effect, the hidden descriptor fields of the segment registers function as the memory management cache of the 80286. All the information required to address the current working set of segments~that is, the base address, size, and access rights of the currently addressable

Most memory references do not require the translation of a full

In fact, .most 80286 instructions reference memory locations in precisely this way, specifying only a

ICPii:----- --- ----- ,

APPLICATION |

|

| DESCRIPTOR | SYSTEM |

VISIBLE |

| - | CACHE | MEMORY |

SEGMENT |

| SEGMENT |

| |

REGISTER |

|

|

|

|

| ||||

I SELE~TOR | I |

| TYPE |

|

1BASE

1

.1 | LIMIT |

| |

I |

|

| |

1 | TRANSPARENT |

| |

I |

| ||

DESCRIPTOR |

| ||

1 | LOADING | I | |

| |||

1 |

| I | |

I |

| ||

|

| ||

L __ _ |

| I | |

r | |||

| |||

|

|

DESCRIPTOR TABLE

I

I

_______

G30108