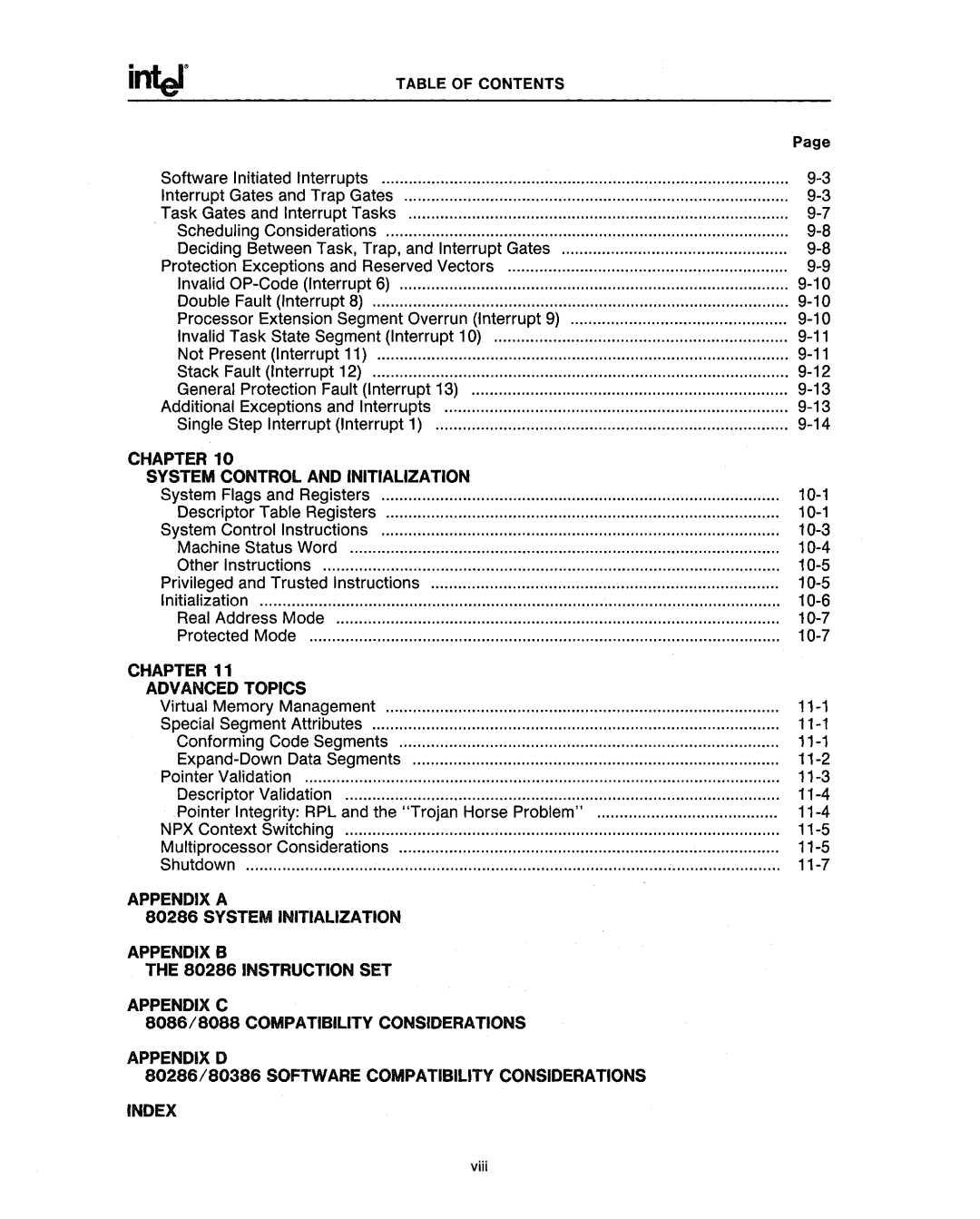

TABLE OF CONTENTS |

|

|

|

| Page |

Software Initiated Interrupts | ||

Interrupt Gates and Trap Gates | ||

Task Gates and Interrupt Tasks | ||

Scheduling Considerations | ||

Deciding Between Task, Trap, and Interrupt Gates | ||

Protection Exceptions and Reserved Vectors | ||

Invalid | ||

Double Fault (Interrupt 8) | ||

Processor Extension Segment Overrun (Interrupt 9) | ||

Invalid Task State Segment (Interrupt 10) | ||

Not Present (Interrupt 11) | ||

Stack Fault (Interrupt 12) | ||

General Protection Fault (Interrupt 13) | ||

Additional Exceptions and Interrupts | ||

Single Step Interrupt (Interrupt 1) | ||

CHAPTER 10 |

|

|

SYSTEM CONTROL AND INITIALIZATION |

|

|

System Flags and Registers |

| |

Descriptor Table Registers | ||

System Control Instructions |

| |

Machine Status Word |

| |

Other Instructions |

| |

Privileged and Trusted Instructions | ||

Initialization |

| |

Real Address Mode |

| |

Protected Mode | ||

CHAPTER 11 |

|

|

ADVANCED TOPICS |

|

|

Virtual Memory Management |

| |

Special Segment Attributes | ||

Conforming Code Segments | ||

| ||

Pointer Validation |

| |

Descriptor Validation |

| |

Pointer Integrity: RPL and the "Trojan Horse Problem" | ||

NPX Context Switching |

| |

Multiprocessor Considerations | ||

Shutdown | ; |

|

APPENDIX A

80286 SYSTEM INITIALIZATION

APPENDIX B

THE 80286 INSTRUCTION SET

APPENDIX C

8086/8088 COMPATIBILITY CONSIDERATIONS

APPENDIX D

80286/80386 SOFTWARE COMPATIBILITY CONSIDERATIONS

INDEX

viii