PROGRAMMING NUMERIC APPLICATIONS

Instruction execution by the 80287 NPX

Operand transfers between the 80287 NPX and memory or a CPU register

The timing of these various activities is affected by the individual clock frequencies of the 80286 CPU and the 80287 NPX. In addition, slow memories requiring the insertion of wait states in bus cycles, and bus contention due to other processors in the system, may lengthen operand transfer times.

In calculating an overall execution time for an individual numeric instruction, analysts must take each of these activities into account. In most cases, it can be assumed that the numeric instructions have already been prefetched by the 80286 and are awaiting execution.

•The CPU overhead in handling the ESC instruction opcode takes only a single CPU bus cycle before the 80287 begins its execution of the numeric instruction. The timing of this bus cycle is determined by the CPU clock. Additional CPU activity is required to set up the 80287's instruction and data pointer registers, but this activity occurs after the 80287 has begun executing its instruc- tion, and so this parallel activity does not affect total execution time.

•The duration of individual numeric instructions executing on the 80287 varies for each instruction. Table

•The operand transfer time required to transfer operands between the 80287 and memory or a CPU register depends on the number of words to be transferred, the frequency of the CPU clock control- ling bus timing, the number of wait statcs added to accommodate slower memories, and whether operands are based at even or odd memory addresses. Some (small) additional number of bus cycles may also be lost due to the asynchronous nature of the PEREQ/PEACK handshaking between the 80286 and 80287, and this interaction varies with relative frequencies of the CPU and NPX clocks.

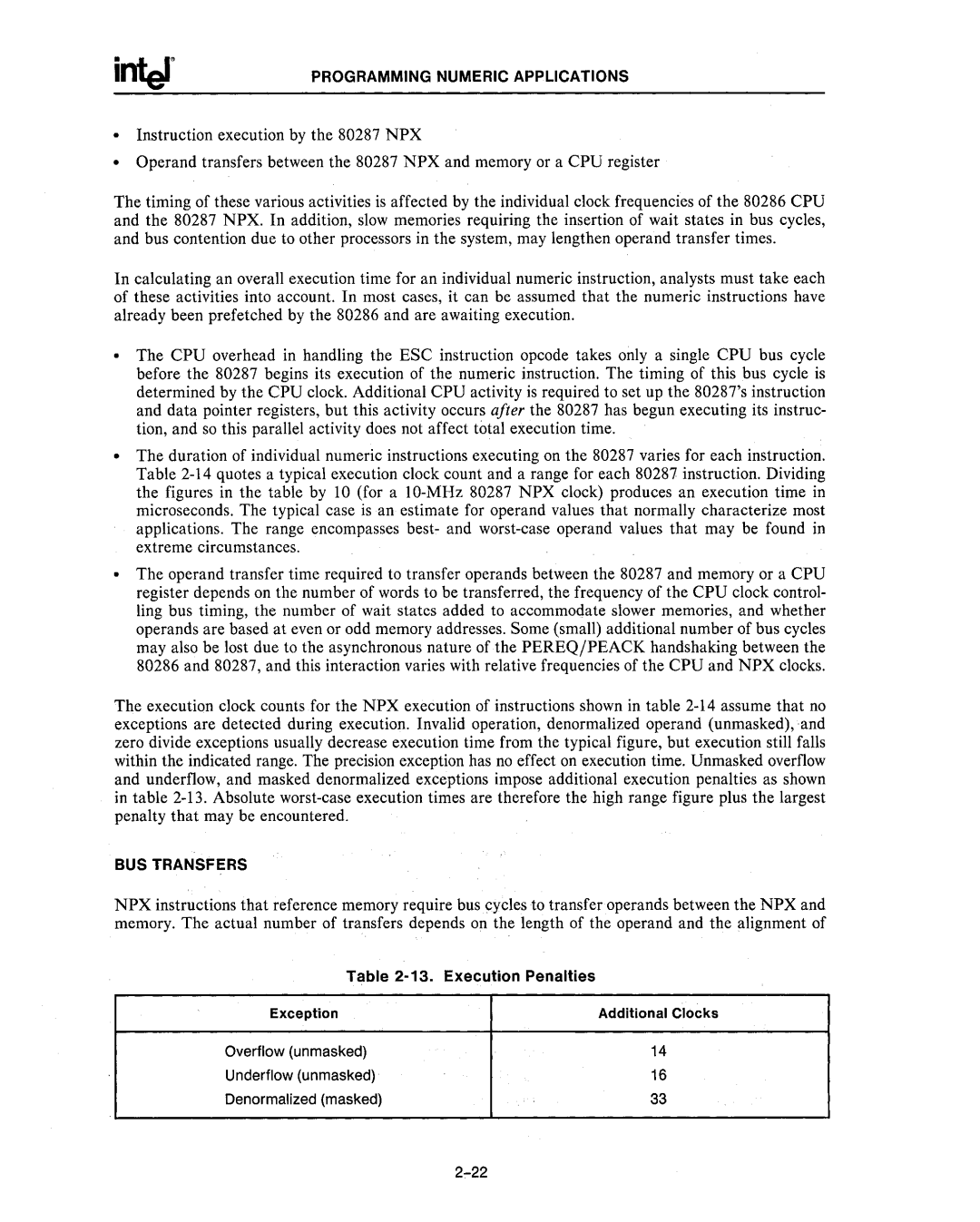

The execution clock counts for the NPX execution of instructions shown in table

BUS TRANSFERS

NPX instructions that reference memory require bus cycles to transfer operands between the NPX and memory. The actual number of transfers depends on the length of the operand and the alignment of

Table 2-13. Execution Penalties

Exception | Additional Clocks |

Overflow (unmasked) | 14 |

Underflow (unmasked) | 16 |

Denormalized (masked) | 33 |