TASKS AND STATE TRANSITIONS

Note that the state of the outgoing task is always saved. If execution of that task is resumed, it will start after the instruction that caused the task switch. The values of the registers will be the same as that when the task stopped running.

Any task switch sets the Task Switched (TS) bit in the Machine Status Word (MSW). This flag is used when processor extensions such as the 80287 Numeric Processor Extension are present. The TS bit signals that the context of the processor extension may not belong to the current 80286 task. Chapter 11 discusses the TS bit and processor extensions in more detail.

Validity tests on a selector ensure that the selector is in the proper table (i.e., the LDT selector refers to GDT), lies within the bounds of the table, and refers to the proper type of descriptor (i.e., the LDT selector refers to the LDT descriptor).

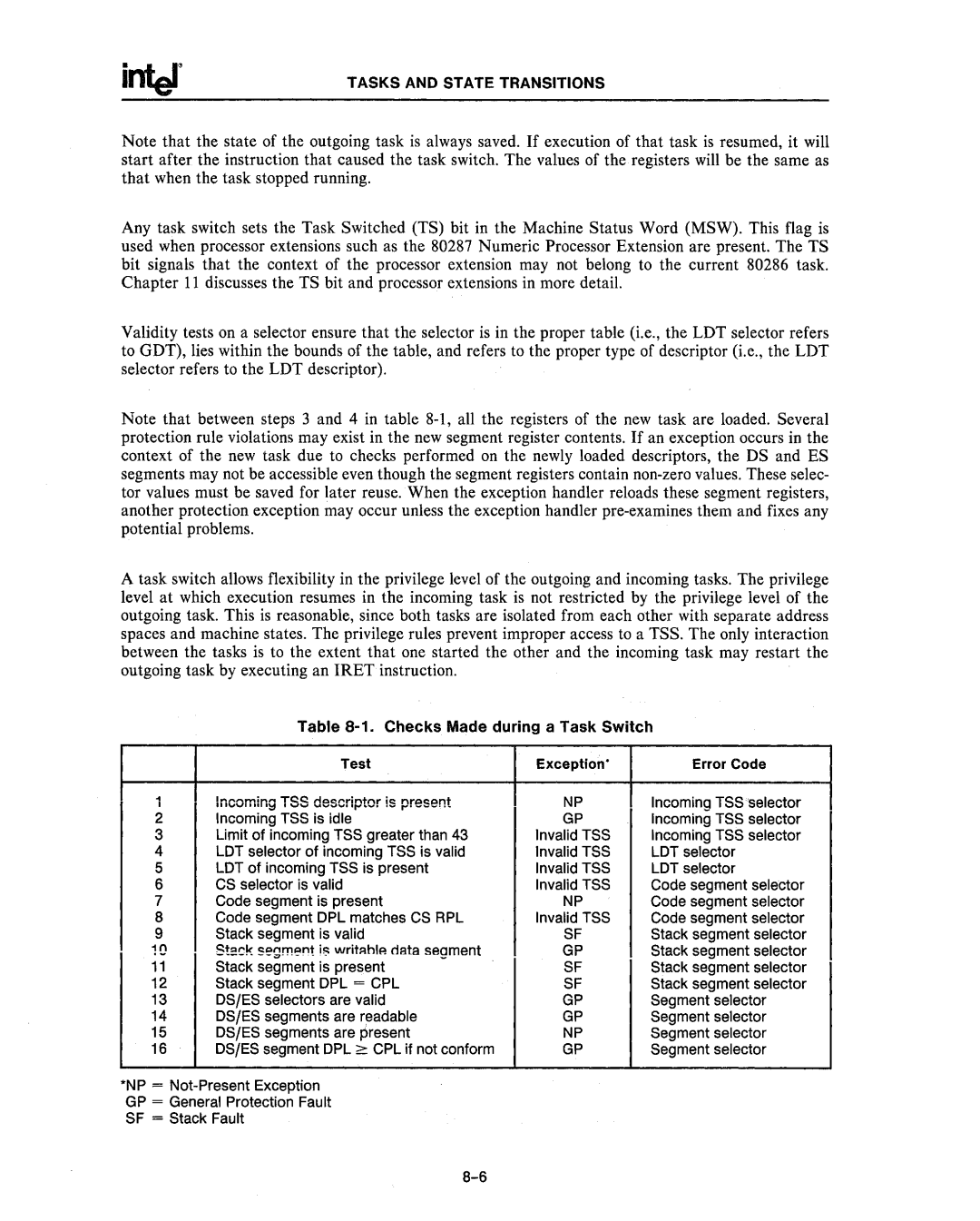

Note that between steps 3 and 4 in table

A task switch allows flexibility in the privilege level of the outgoing and incoming tasks. The privilege level at which execution resumes in the incoming task is not restricted by the privilege level of the outgoing task. This is reasonable, since both tasks are isolated from each other with separate address spaces and machine states. The privilege rules prevent improper access to a TSS. The only interaction between the tasks is to the extent that one started the other and the incoming task may restart the outgoing task by executing an IRET instruction.

Table 8-1. Checks Made during a Task Switch

.

I

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

*NP = GP = SF =

Test | Exception' | Error Code |

Incoming TSS descriptor is present | NP | Incominq TSS'selector |

Incoming TSS is idle | GP | Incoming TSS selector |

Limit of incoming TSS greater than 43 | Invalid TSS | Incoming TSS selector |

LOT selector of incoming TSS is valid | Invalid TSS | LOT selector |

LOT of incoming TSS is present | Invalid TSS | LOT selector |

CS selector is valid | Invalid TSS | Code segment selector |

Code segment is present | NP | Code segment selector |

Code segment OPL matches CS RPL | Invalid TSS | Code segment selector |

Stack segment is valid | SF | Stack segment selector |

St~ck segment i", writ::lhlp. data segment | GP | Stack segment selector |

Stack segment is present | SF | Stack segment selector |

Stack segment OPL = CPL | SF | Stack segment selector |

OS/ES selectors are valid | GP | Segment selector |

OS/ES segments are r!3adable | GP | Segment selector |

OS/ES segments are present | NP | Segment selector |

OS/ES segment OPL ;::: CPL if not conform | GP | Segment selector |

|

| |

General Protection Fault |

|

|

Stack Fault |

|

|