INTERRUPTS AND EXCEPTIONS

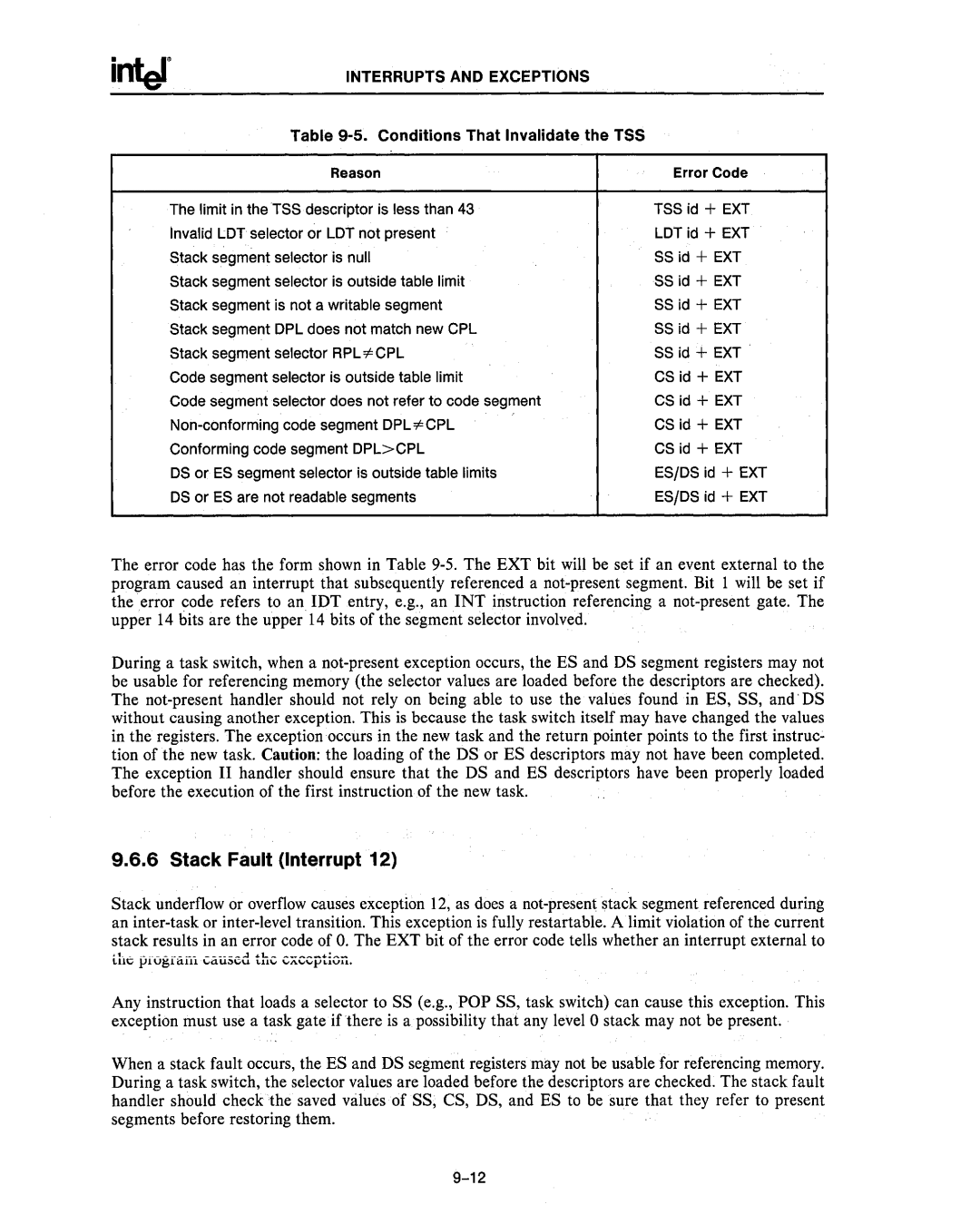

Table 9-5. Conditions That Invalidate the TSS

Reason | Error Code |

The limit in theTSSdescriptor is less than 43 | TSS id + EXT |

Invalid LOT selector or LOT not present | LOTid + EXT |

Stack segment selector is null | SS id + EXT |

Stack segment selector is outside table limit | SS id + EXT |

Stack segment is not a writable segment | SS id + EXT |

Stack segment OPL does not match new CPL | SS id + EXT |

Stack segment selector RPL;6CPL | SS id + EXT |

Code segment selector is outside table limit | CS id + EXT |

Code segment selector does not refer to code segment | CS id + EXT |

CS id + EXT | |

Conforming code segment OPL>CPL | CS id + EXT |

OS or ES segment selector is outside table limits | ES/OS id + EXT |

OS or ES are not readable segments | ES/OS id + EXT |

The error code has the form shown in Table

upper 14 bits are the upper 14 bits of the segment selector involved. | . |

During a task switch, when a

9.6.6 Stack Fault (Interrupt 12)

Stack underflow or overflow causes exception 12, as does a

Any instruction that loads a selector to SS (e.g., POP SS, task switch) can cause this exception. This exception must use a task gateifthere is a possibility that any level 0 stack may not be present.

When a stack fault occurs, the ES and DS segment registers may not be usable for referencing memory. During a task switch, the selector values are loaded before the descriptors are checked. The stack fault handler should check the saved values <if SS, CS, DS, and ES to be sure that they refer to present segments before restoring them.