INTERRUPTS AND EXCEPTIONS

Each IDT entry is a

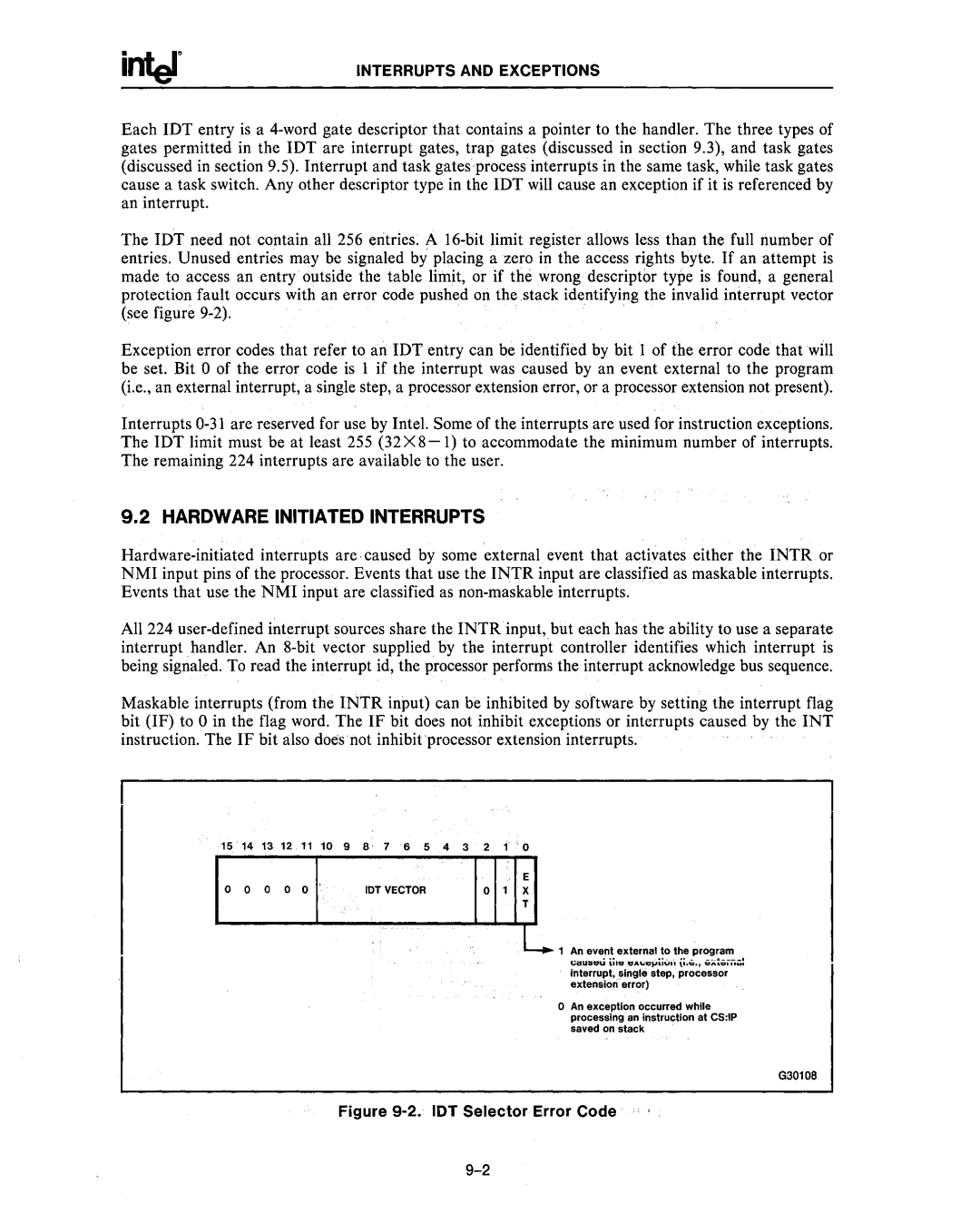

The IDT need not contain all 256 entries: A

(see figure | .. |

Exception error codes that tefer to an IDT entry can be identified by bit 1 of the error code that will be set. Bit 0 of the error code is 1 if the interrupt was caused by an event external to the program (Le., an external interrupt, a single step, a processor extension error, ora processor extension not present).

Interrupts

9.2 HARDWARE INITIATED INTERRUPTS

Events that use the NMI input are classified as

All 224

Maskable interrupts (from the INTR input) can be inhibited by software by setting the interrupt flag bit (IF) to 0 in the flag word. The IF bit does not inhibit exceptions or interrupts caused by the INT instruction. The IF bit also does· IiOt inhibit processor extension interrupts.

15·14 13 12.11 10 9 8: 7 ·6 5 4 3 ·2 1·; 0

E

0 0 0 0 o· IDTVECTOR0 1 X T

1 An eve."! eXtern8~.~~__t~~_pr~~_~~~_1

fiOIIUtf"U "1e11 ."~'CII"ILIUII v .•. , ...... ,..........

Interrupt, ,Bingle step, processor extension'error)

o An exception occurred while

procesSing'an instruction at CS:IP saved on stack

G30108