OVERVIEW OF NUMERIC PROCESSING

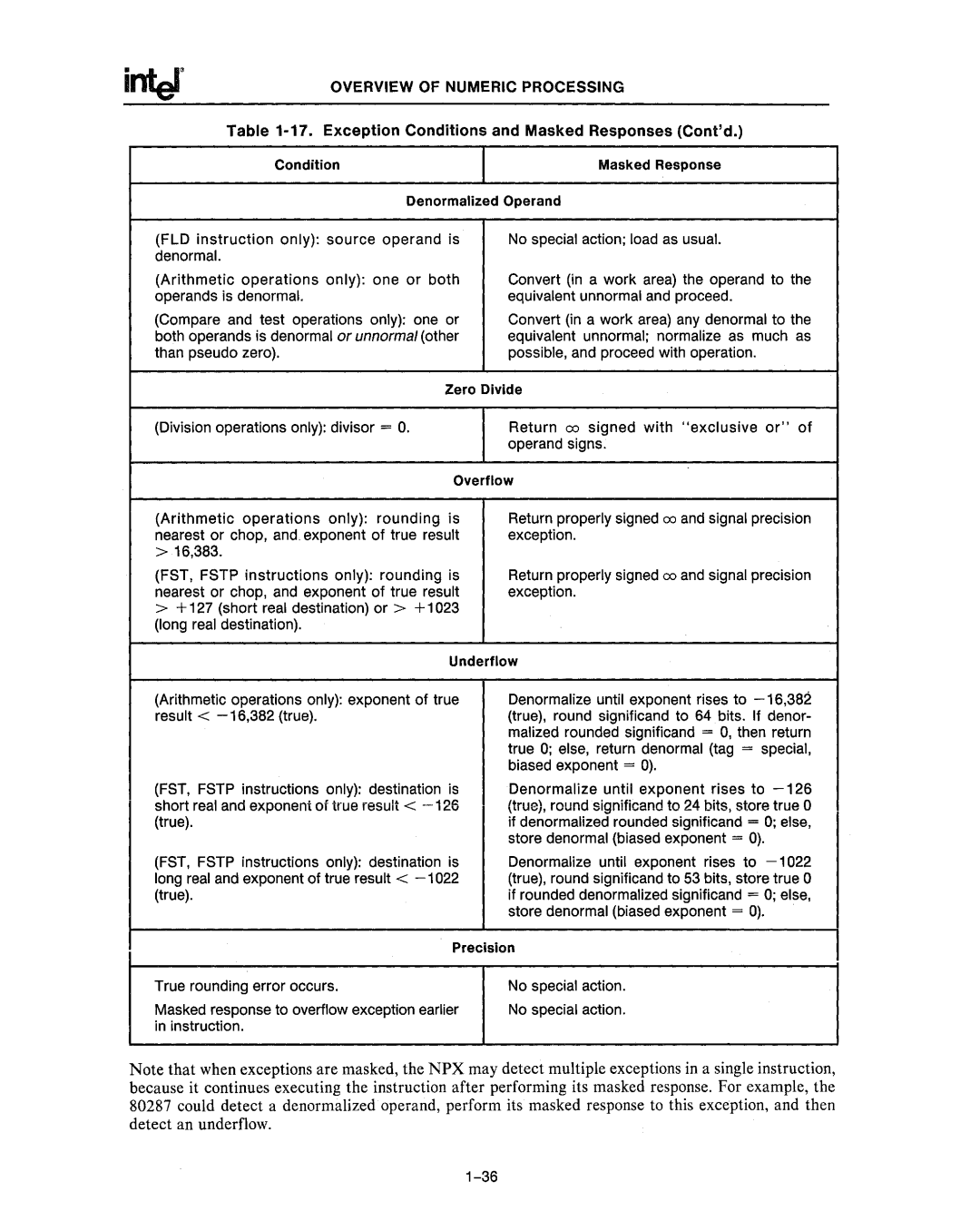

Table 1-17. Exception Conditions and Masked Responses (Cont'd.)

Condition | Masked Response |

Denormalized Operand

(FLD instruction only): source operand is denormal.

(Arithmetic operations only): one or both operands is denormal.

(Compare and test operations only): one or both operands is denormal or unnormal (other than pseudo zero).

No special action; load as usual.

Convert (in a work area) the operand to the equivalent unnormal and proceed.

Convert (in a work area) any denormal to the equivalent unnormal; normalize as much as possible, and proceed with operation.

Zero Divide

(Division operations only): divisor = O.

Return 00 signed with "exclusive or" of operand signs;

Overflow

(Arithmetic operations only): rounding is nearest or chop, and. exponent of true result

>16,383.

(FST, FSTP instructions only): rounding is nearest or chop, and exponent of true result

>+127 (short real destination) or> +1023 (long real destination).

Return properly signed 00 and signal precision exception.

Return properly signed 00 and Signal precision exception.

Underflow

(Arithmetic operations only): exponent of true result <

(FST, FSTP instructions only): destination is short real and exponent of true result <

(FST, FSTP instructions only): destination is long real and exponent of true result <

Denormalize until exponent rises to

Denormalize until exponent rises to

Denormalize until exponent rises to

Precision | |

True rounding error occurs. | No special action. |

Masked response to overflow exception earlier | No special action. |

in instruction. |

|

Note that when exceptions are masked, the NPX may detect multiple exceptions in a single instruction, because it continues executing the instruction after performing its masked response. For example, the 80287 could detect a denormalized operand, perform its masked response to this exception, and then detect an underflow.