80286 BASE ARCHITECTURE

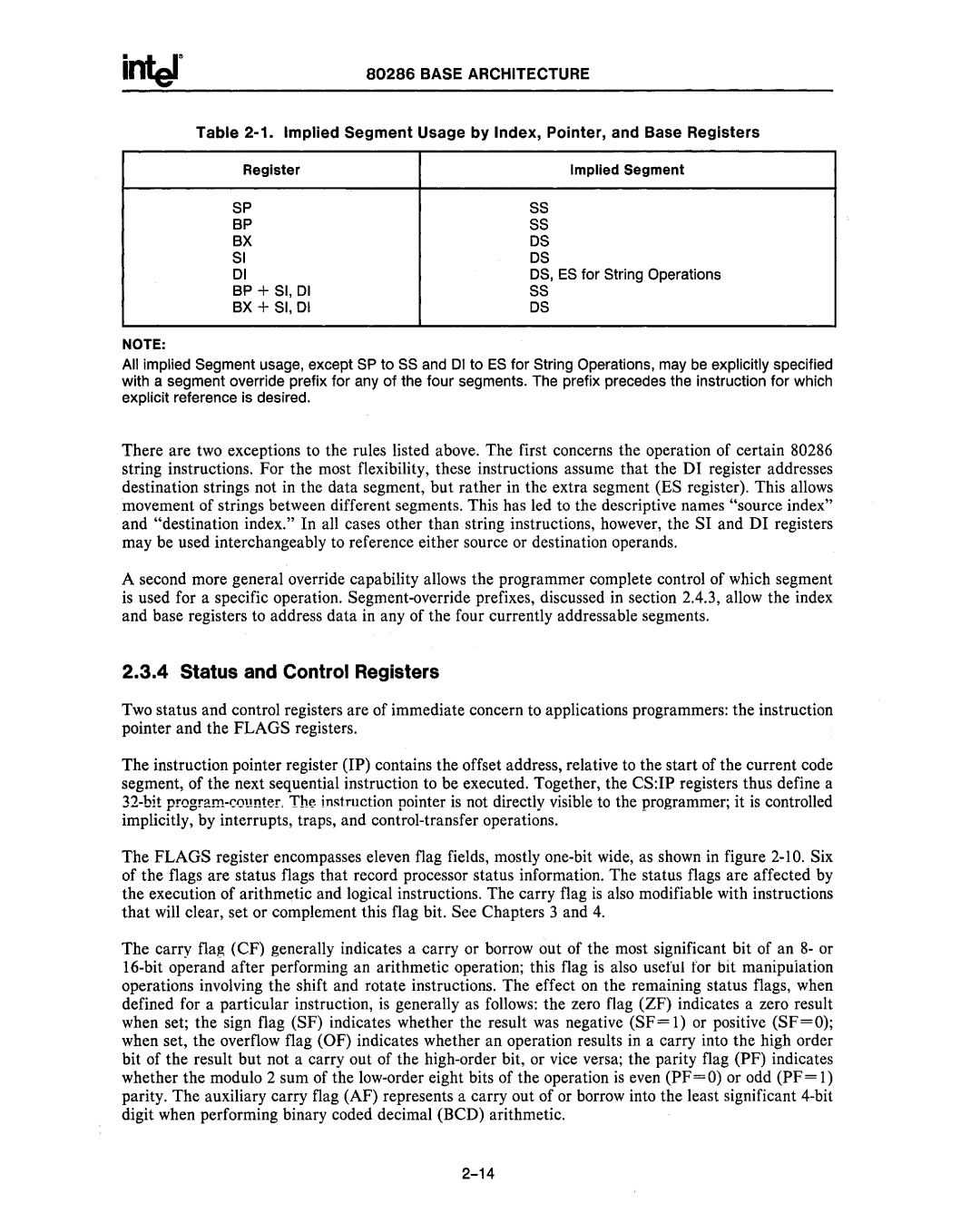

Table 2-1. Implied Segment Usage by Index, Pointer, and Base Registers

Register | Implied Segment |

SP | 55 |

BP | SS |

BX | OS |

SI | OS |

01 | OS, ES for String Operations |

BP + 51, 01 | SS |

BX + SI, 01 | OS |

NOTE:

All implied Segment usage, except SP to SS and 01 to ES for String Operations, may be explicitly specified with a segment override prefix for any of the four segments. The prefix precedes the instruction for which explicit reference is desired.

There are two exceptions to the rules listed above. The first concerns the operation of certain 80286 string instructions. For the most flexibility, these instructions assume that the DI register addresses destination strings not in the data segment, but rather in the extra segment (ES register). This allows movement of strings between different segments. This has led to the descriptive names "source index" and "destination index." In all cases other than string instructions, however, the SI and DI registers may be used interchangeably to reference either source or destination operands.

A second more general override capability allows the programmer complete control of which segment is used for a specific operation.

2.3.4 Status and Control Registers

Two status and control registers are of immediate concern to applications programmers: the instruction pointer and the FLAGS registers.

The instruction pointer register (IP) contains the offset address, relative to the start of the current code segment, of the next sequential instruction to be executed. Together, the CS:IP registers thus define a

The FLAGS register encompasses eleven flag fields, mostly

The carry flag (CF) generally indicates a carry or borrow out of the most significant bit of an 8- or