BASIC INSTRUCTION SET

01, I, I aI a1,1, I, I, I a1,1,1, I aI alai'I

BEFORE SHR

01 aI, I, I aI aI, I, I, I, I aI, I, 1,1 aI aI aI--Q~~;~:Y

AFTER

SHR BY

10 BITS

OF | OPERAND | CF |

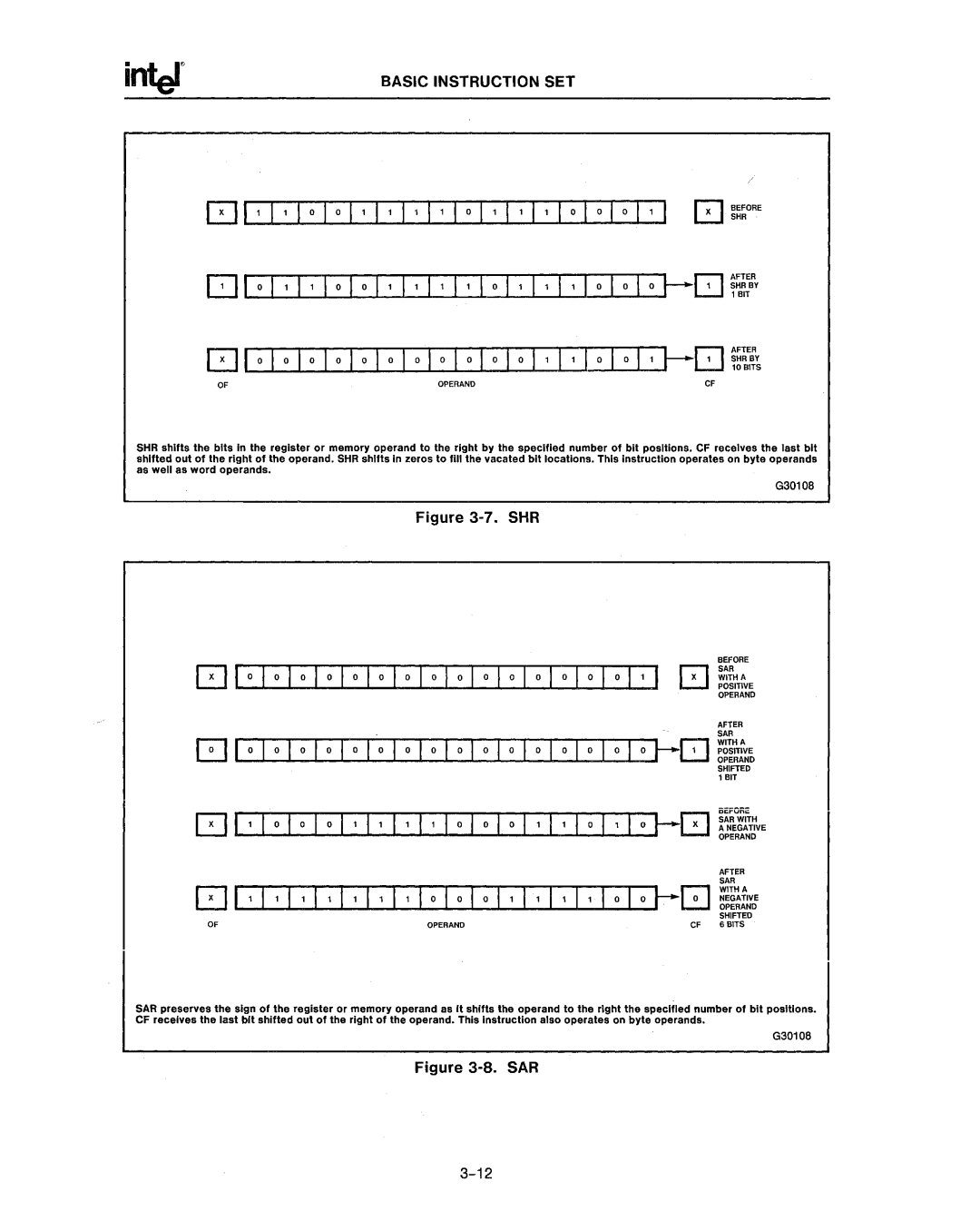

SHR shilts the bits In the register or memory operand to the right by the specified number of bit positions. CF receives the last bit shifted out of the right of the operand. SHR shifts in zeros to fill the vacated bit locations. This instruction operates on byte operands as well as word operands.

G30108

Figure 3-7. SHR

Dlalalalalalalalalalalalalalalal'l

c:J I aI aI aI aI ala I aI aI aI aI aI aI aI aI aI

01, I aI aI aI, I, I, I, I aI aI aI, I, I aI, I a1--0

BEFORE

SAR

WITH A

POSITIVE OPERAND

AFTER

SAR

WITH A

POSITIVE OPERAND SHIFTED

1 BIT

iii:;r=Cn::'

SARWITH

ANEGATIVE OPERAND

D I, I, I, I, I, I, I, 1a1a1aI, I, I, I, | AFTER | |

SAR | ||

WITHA | ||

NEGATIVE | ||

OPERAND | ||

|

| SHIFTED |

OF | OPERAND | CF 6DITS |

SAR preserves the Sign 01 the register or memory operand as It shifts the operand to the right the specified number of bit positions. CF receives the last bit shifted out of the right of the operand. This instruction also operates on byte operands.

G30108