inl:el® | 80286 BASE ARCHITECTURE |

| SEG 3FFF |

| SEG 3FFE |

| SEG 3FFD |

| SEG 3FFC |

, | SEG 3FFB |

1 GIGABYTE | |

| VIRTUAL ADDRESS |

| SPACE |

I SELECTOR I

SEG 4

SEG 3

1 TO 64K BYTES { | SEG 2 |

| SEG 1 |

| SEG 0 |

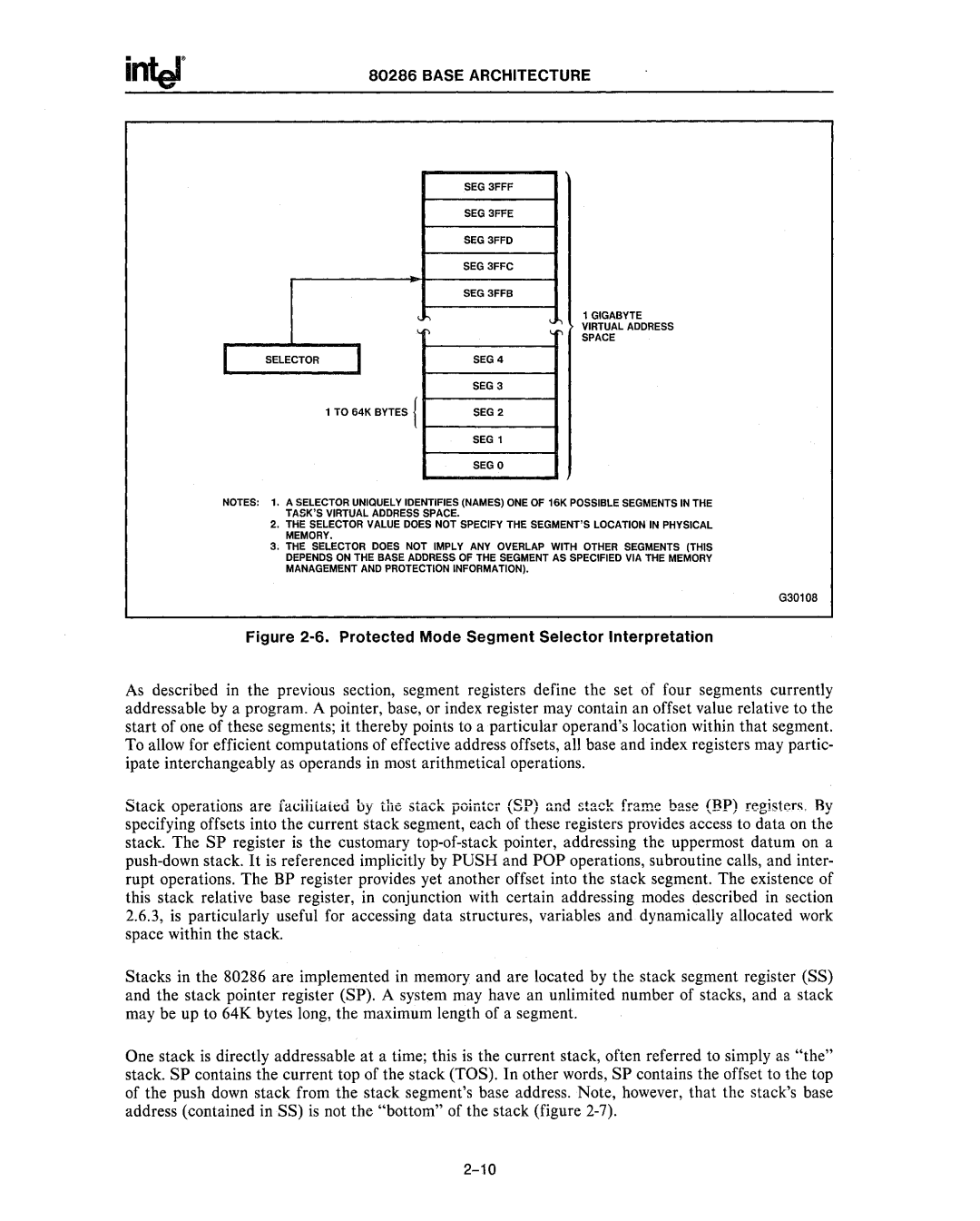

NOTES: 1. A SELECTOR UNIQUELY IDENTIFIES (NAMES) ONE OF 16K POSSIBLE SEGMENTS IN THE

TASK'SVIRTUAL ADDRESS SPACE.

2.THE SELECTOR VALUE DOES NOT SPECIFY THE SEGMENT'SLOCATION IN PHYSICAL MEMORY.

3.THE SELECTOR DOES NOT IMPLY ANY OVERLAP WITH OTHER SEGMENTS (THIS DEPENDS ON THE BASE ADDRESS OF THE SEGMENT AS SPECIFIED VIA THE MEMORY MANAGEMENT AND PROTECTION INFORMATION).

G3010B

Figure 2-6. Protected Mode Segment Selector Interpretation

As described in the previous section, segment registers define the set of four segments currently addressable by a program. A pointer, base, or index register may contain an offset value relative to the start of one of these segments; it thereby points to a particular operand's location within that segment. To allow for efficient computations of effective address offsets, all base and index registers may partic- ipate interchangeably as operands in most arithmetical operations.

Stack operations are facililattd by the stack pointer (SP) ~nd stack frame base (BP) register~_ By specifying offsets into the current stack segment, each of these registers provides access to data on the stack. The SP register is the customary

Stacks in the 80286 are implemented in memory and are located by the stack segment register (SS) and the stack pointer register (SP). A system may have an unlimited number of stacks, and a stack may be up to 64K bytes long, the maximum length of a segment.

One stack is directly addressable at a time; this is the current stack, often referred to simply as "the" stack. SP contains the current top of the stack (TOS). In other words, SP contains the offset to the top of the push down stack from the stack segment's base address. Note, however, that the stack's base address (contained in SS) is not the "bottom" of the stack (figure