THE 80286 INSTRUCTION SET

POP-Pop a Word from the Stack

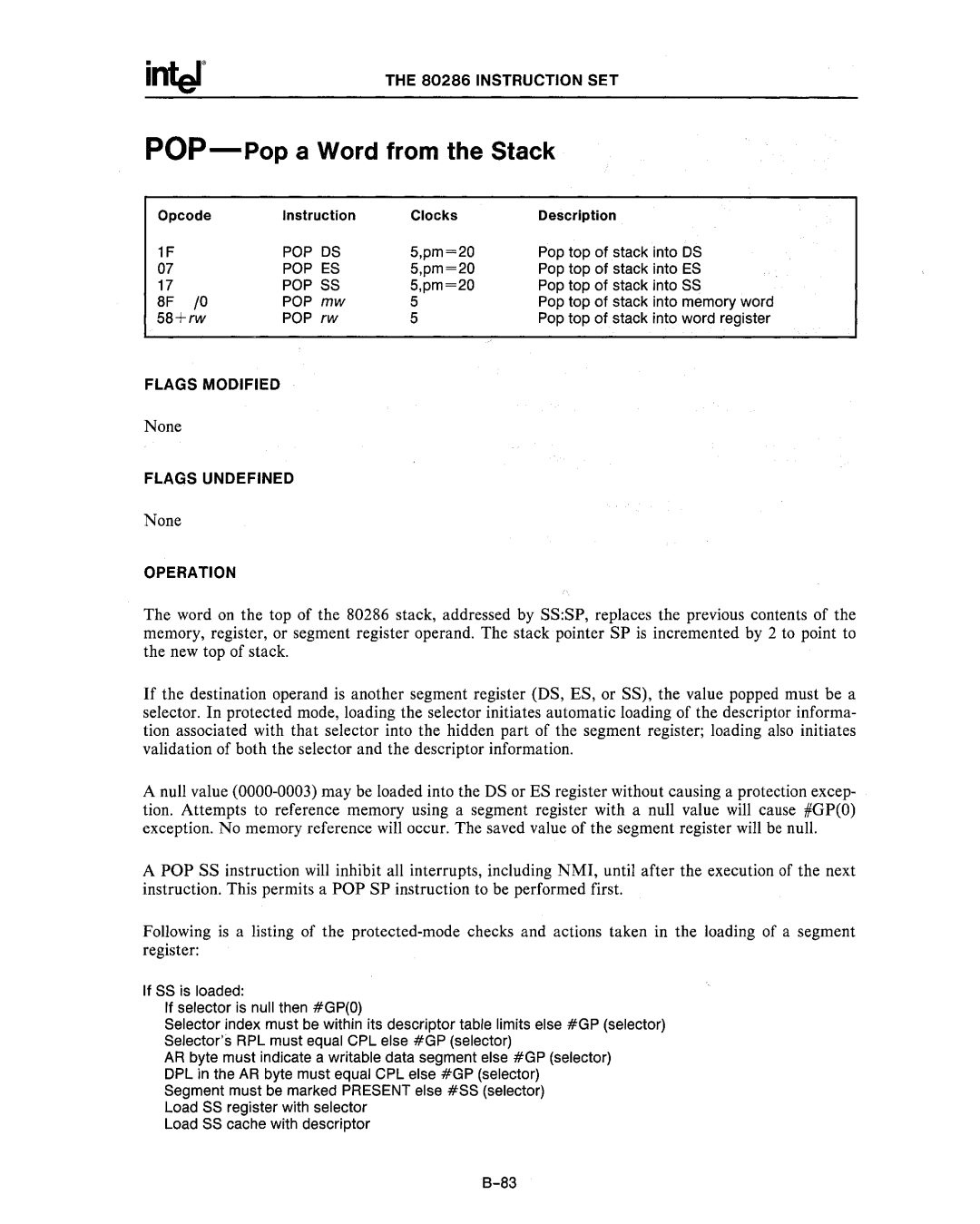

Opcode | Instruction | Clocks | Description | |

1F | POP | OS | 5,pm=20 | Pop top of stack into OS |

07 | POP | ES | 5,pm=20 | Pop top of stack into ES |

17 | POP SS | 5,pm=20 | Pop top of stack into SS | |

SF /0 | POP | mw | 5 | Pop top of stack into memory word |

58+rw | POP | rw | 5 | Pop top of stack into word register |

FLAGS MODIFIED

None

FLAGS UNDEFINED

None

OPERATION

The word on the top of the 80286 stack, addressed by SS:SP, replaces the previous contents of the memory, register, or segment register operand. The stack pointer SP is incremented by 2 to point to the new top of stack.

If the destination operand is another segment register (DS, ES, or SS), the value popped must be a selector. In protected mode, loading the selector initiates automatic loading of the descriptor informa- tion associated with that selector into the hidden part of the segment register; loading also initiates validation of both the selector and the descriptor information.

A null value

A POP SS instruction will inhibit all interrupts, including NMI, until after the execution of the next instruction. This permits a POP SP instruction to be performed first.

Following is a listing of the

If SS is loaded:

If selector is null then #GP(O)

Selector index must be within its descriptor table limits else #GP (selector)

Selector'sRPL must equal CPL else #GP (selector)

AR byte must indicate a writable data segment else #GP (selector)

DPL in the AR byte must equal CPL else #GP (selector)

Segment must be marked PRESENT else #SS (selector)

Load SS register with selector

Load SS cache with descriptor