TASKS AND STATE TRANSITIONS

8.4 TASK LINKING

The TSS has a field called "back link" which contains the selector of the TSS of a task that should be restarted when the current task completes. The back link field of an

A task switch initiated by a CALL instruction also points the back link at the outgoing task's TSS. Such task nesting is indicated to programs via the Nested Task (NT) bit in the flag word of the incoming task.

Task nesting is necessary for interrupt functions to be processed as separate tasks. The interrupt function is thereby isolated from all other tasks in the system. To restart the interrupted task, the interrupt handler executes an IRET instruction much in the same manner as an 8086 interrupt handler. The IRET instruction will then cause a task switch to the interrupted task.

Completion of a task occurs when the IRET instruction is executed with the NT bit in the flag word set. The NT bit is automatically set/reset by task switch operations as appropriate. Executing an IRET instruction with NT cleared causes the normal 8086 interrupt return function to be performed, and no task switch occurs.

Executing IRET with NT set causes a task switch to the task defined. by the back link field of the current TSS. The selector value is fetched and verified as pointing to a valid, accessible TSS. The normal task switch operation described in section 8.3 then occurs. After the task switch is complete, the outgoing task is now idle and considered ready to process another interrupt.

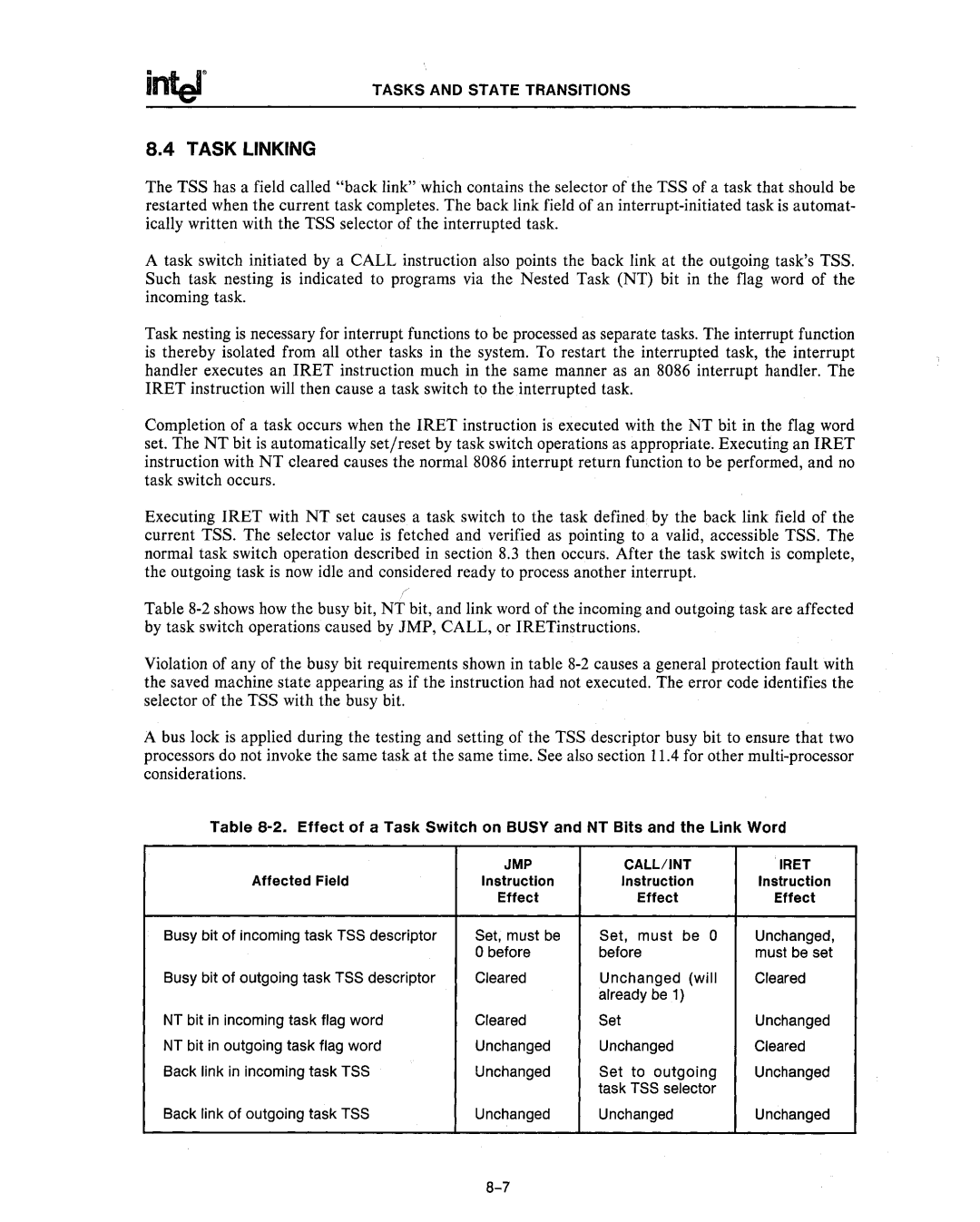

Table

Violation of any of the busy bit requirements shown in table

A bus lock is applied during the testing and setting of the TSS descriptor busy bit to ensure that two processors do not invoke the same task at the same time. See also section 11.4 for other

Table

| JMP | CALL/INT | IRET | |

Affected Field | Instruction | Instruction | Instruction | |

| Effect | Effect |

| Effect |

Busy bit of incoming task TSS descriptor | Set, must be | Set, must | be 0 | Unchanged, |

| obefore | before |

| must be set |

Busy bit of outgoing task TSS descriptor | Cleared | Unchanged | (will | Cleared |

|

| already be 1) |

| |

NT bit in incoming task flag word | Cleared | Set |

| Unchanged |

NT bit in outgoing task flag word | Unchanged | Unchanged |

| Cleared |

Back link in incoming task TSS | Unchanged | Set to outgoing | Unchanged | |

|

| task TSS selector |

| |

Back link of outgoing task TSS | Unchanged | Unchanged |

| Unchanged |