80286 eASE ARCHITECTURE

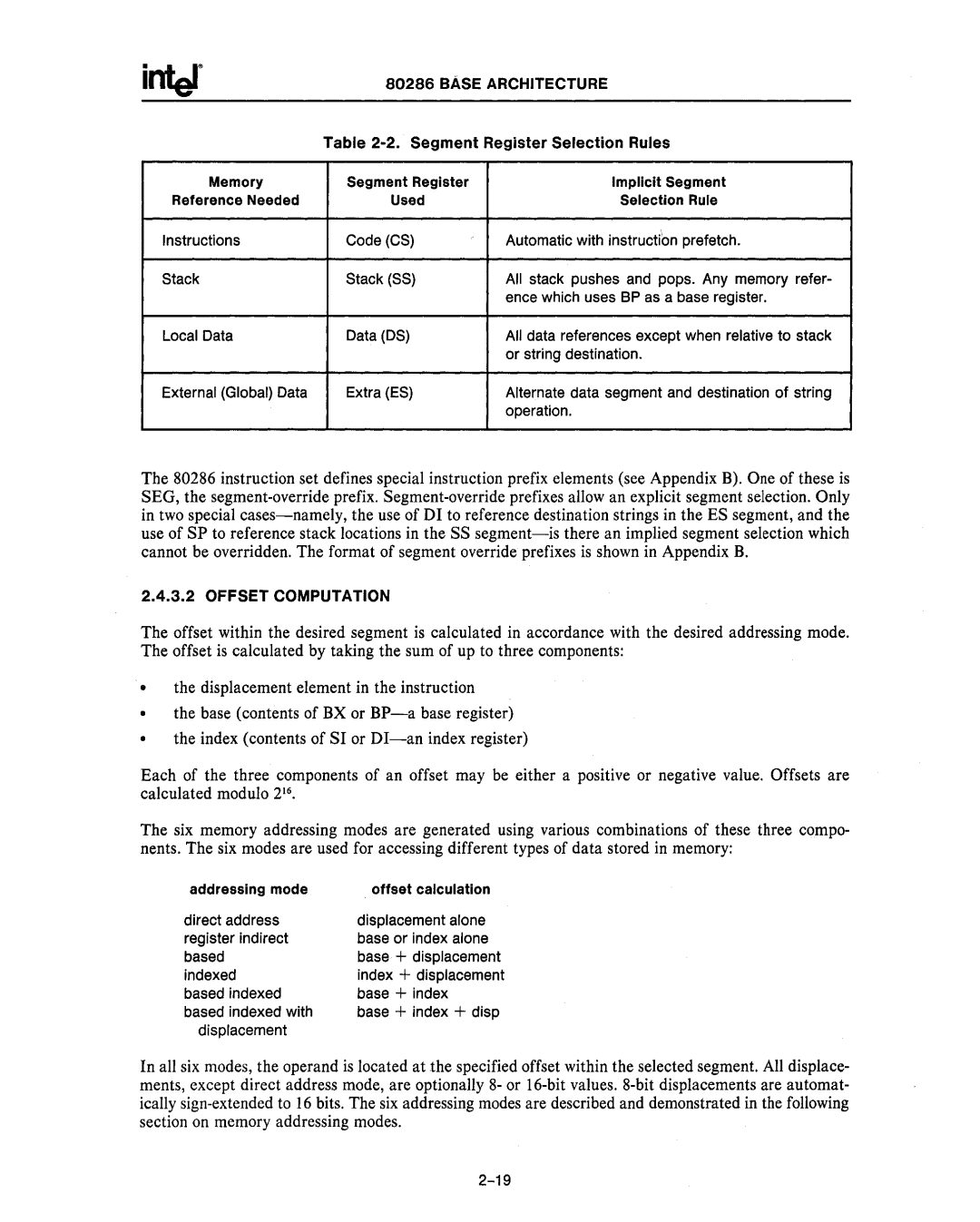

Table 2-2. Segment Register Selection Rules

Memory | Segment Register | Implicit Segment |

Reference Needed | Used | Selection Rule |

Instructions | Code (CS) | Automatic with instruction prefetch. |

Stack | Stack (SS) | All stack pushes and pops. Any memory refer- |

|

| ence which uses BP as a base register. |

Local Data | Data (OS) | All data references except when relative to stack |

|

| or string destination. |

External (Global) Data | Extra (ES) | Alternate data segment and destination of string |

|

| operation. |

The 80286 instruction set defines special instruction prefix elements (see Appendix B). One of these is SEG, the

2.4.3.2 OFFSET COMPUTATION

The offset within the desired segment is calculated in accordance with the desired addressing mode. The offset is calculated by taking the sum of up to three components:

•the displacement element in the instruction

the base (contents of BX or

Each of the three components of an offset may be either a positive or negative value. Offsets are calculated modulo 216.

The six memory addressing modes are generated using various combinations of these three compo- nents. The six modes are used for accessing different types of data stored in memory:

addressing mode | offset calculation |

direct address | displacement alone |

register indirect | base or index alone |

based | base + displacement |

indexed | index + displacement |

based indexed | base + index |

based indexed with | base + index + disp |

displacement |

|

In all six modes, the operand is located at the specified offset within the selected segment. All displace- ments, except direct address mode, are optionally 8- or