SYSTEM CONTROL AND INITIALIZATION

|

|

| CPU |

|

|

| MEMORY | , |

|

|

|

|

|

|

|

| |

|

| 23 | 15 GDTLIMIT | 0 |

| U! | · |

|

|

| J | - |

| I |

| ||

GDTR | I | GDTBASE | I |

|

| |||

|

| 15 |

|

|

| |||

|

|

| LDT |

|

|

| LDTl |

|

|

|

|

|

|

|

|

| |

|

|

| I ~ELECTOR |

|

| I | · |

|

|

| |||||||

| I | CURRENl | ||||||

| I |

| 15 | 0 | I | I | LDT | |

|

|

|

|

| I | |||

|

| I LDTLIMIT | i |

| 1 | |||

| I | 23 |

| |||||

LDTR | I | I | LDTBASE |

| ..J |

|

| |

| I |

| i |

|

|

|

| |

| I |

| I |

| LDTn |

| ||

| I | PROGRAM INVISIBLE |

|

| · |

| ||

| L ________ ....I |

|

| |||||

|

|

|

|

|

|

|

| |

,~

G3010B

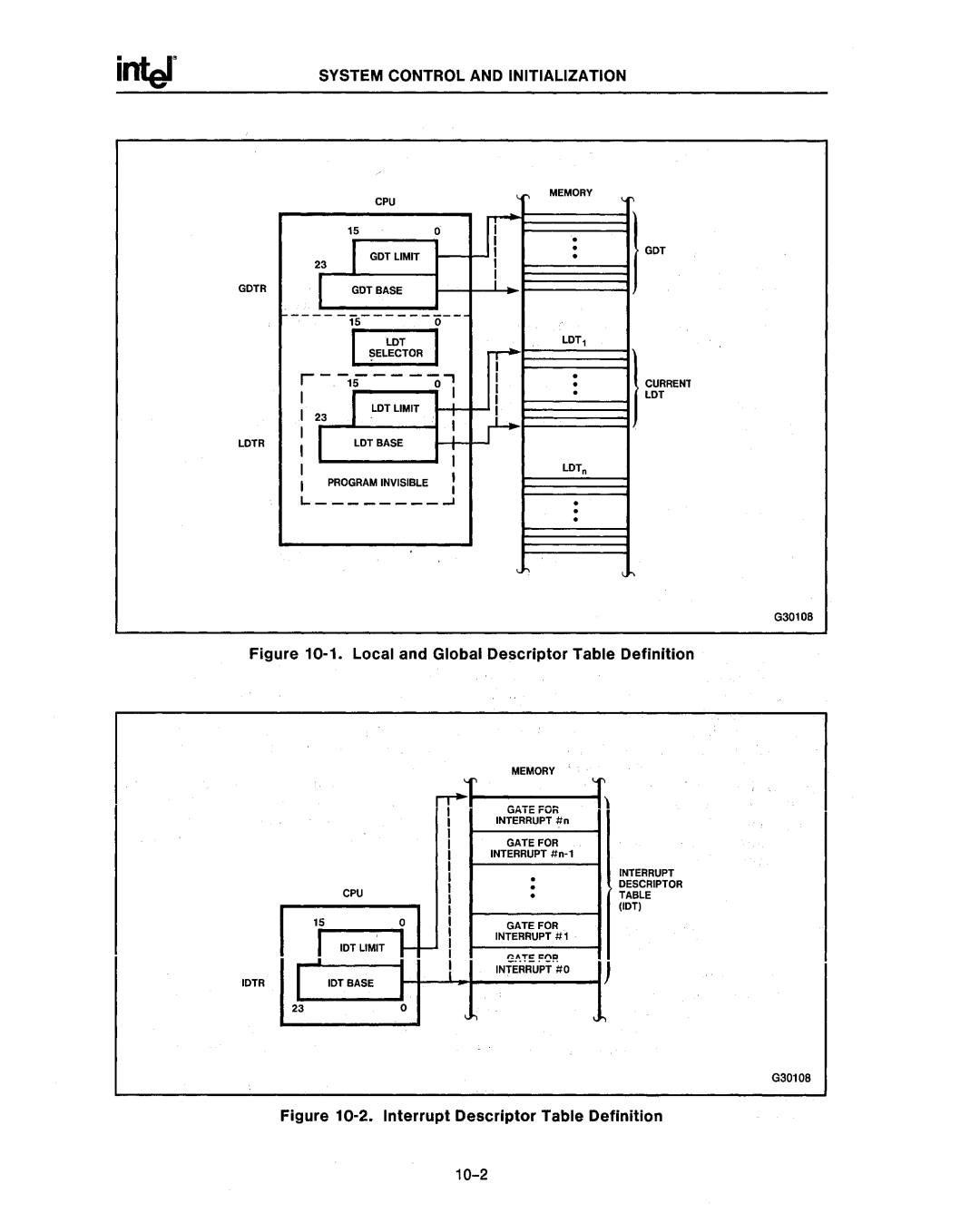

Figure 10-1. Local and Global Descriptor Table Definition

|

|

|

|

| MEMORY |

|

|

|

|

| ! | GATE FOR | \ |

|

|

|

|

| INTERRUPT #n |

|

|

|

|

|

| GATE FOR |

|

|

|

|

|

| INTERRUPT |

|

|

|

|

|

| · | INTERRUPT |

|

|

| CPU |

|

| DESCRIPTOR |

|

|

|

|

| TABLE | |

|

|

|

| o~ |

| (lDT) |

|

| 15 |

| GATE FOR |

| |

|

| J | IDTLIMIT | INTERRUPT #1 |

| |

| I |

|

| ~~T!:!=~~ | J | |

|

| i | INTERRUPT #0 | |||

IDTR | IDT BASE |

| ||||

|

| |||||

| 23 |

|

| 0 |

| ,., |

G3010B