REAL ADDRESS MODE

POINTER TO

INTERRUPT HANDLER

FOR:

INTERRUPT 255 | POINTER |

INTERRUPT 254 | POINTER |

INTERRUPT 253 | POINTER |

| ~ |

INTERRUPT 1 | POINTER |

| |

INTERRUPT 0 | POINTER |

PHYSICAL

ADDRESS

| 1020 |

|

|

|

|

|

|

|

|

.. | 1016 |

|

|

|

|

|

|

|

|

1012 |

|

|

|

|

|

|

|

| |

~~ | 0 | • | .. .... |

| I | VECTOR |

| 101 oj | |

1 |

|

| 01 |

|

|

|

| ||

| 19 |

| 10 | 9 |

| 2 | 1 | 0 | |

4

0

G3010a

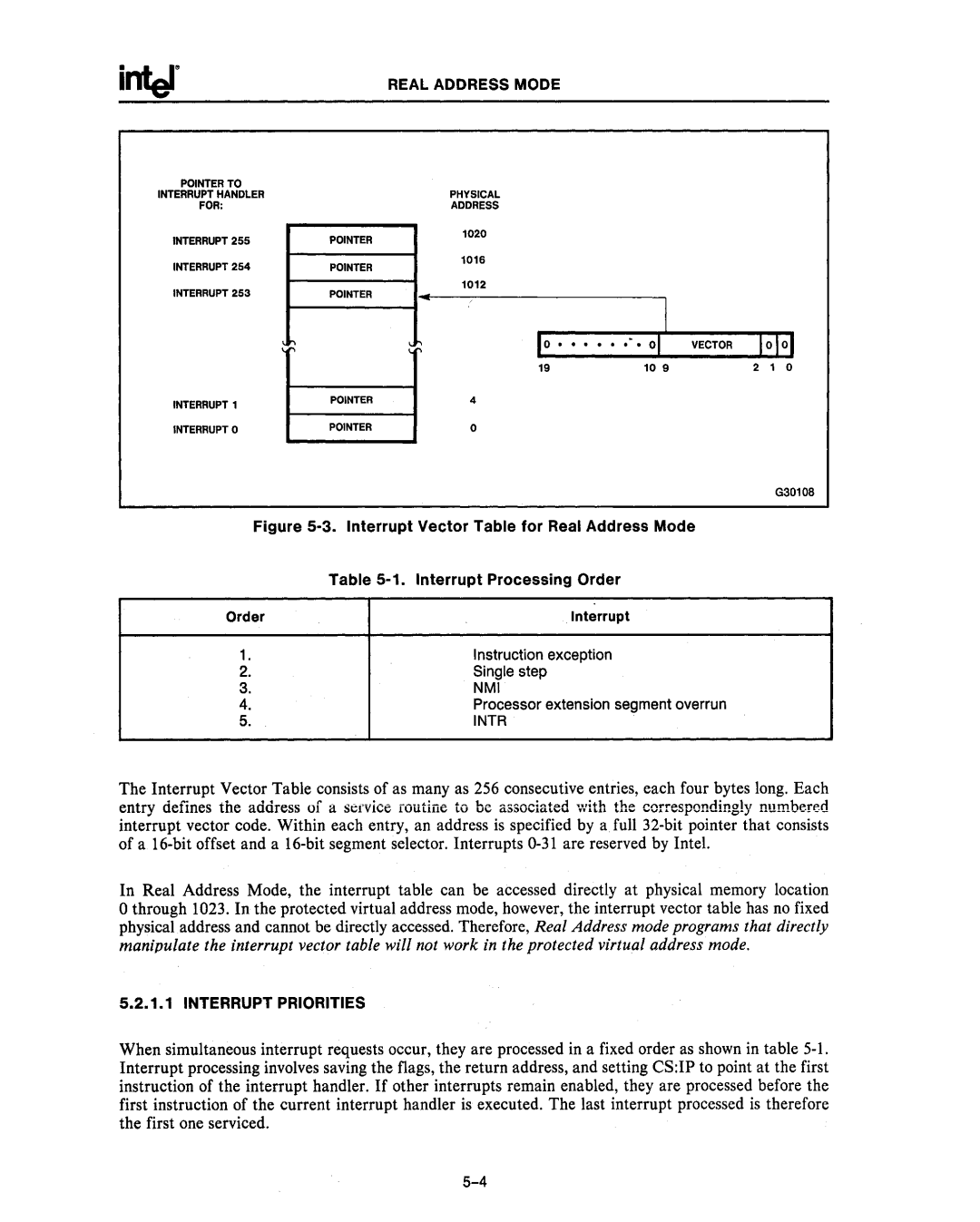

Figure 5-3. Interrupt Vector Table for Real Address Mode

| Table |

Order | Interrupt |

1. | Instruction exception |

2. | Single step |

3. | NMI |

4. | Processor extension segment overrun |

5. | INTR |

The Interrupt Vector Table consists of as many as 256 consecutive entries, each four bytes long. Each entry defines the address of a service routine to be associated \vith the correspondingly numbered interrupt vector code. Within each entry, an address is specified by a full

In Real Address Mode, the interrupt table can be accessed directly at physical memory location othrough 1023. In the protected virtual address mode, however, the interrupt vector table has no fixed physical address and cannot be directly accessed. Therefore, Real Address mode programs that directly manipulate the interrupt vector table will not work in the protected virtual address mode.

5.2.1.1 INTERRUPT PRIORITIES

When simultaneous interrupt requests occur, they are processed in a fixed order as shown in table