THE 80286 INSTRUCTION SET

CMC-Complement Carry Flag

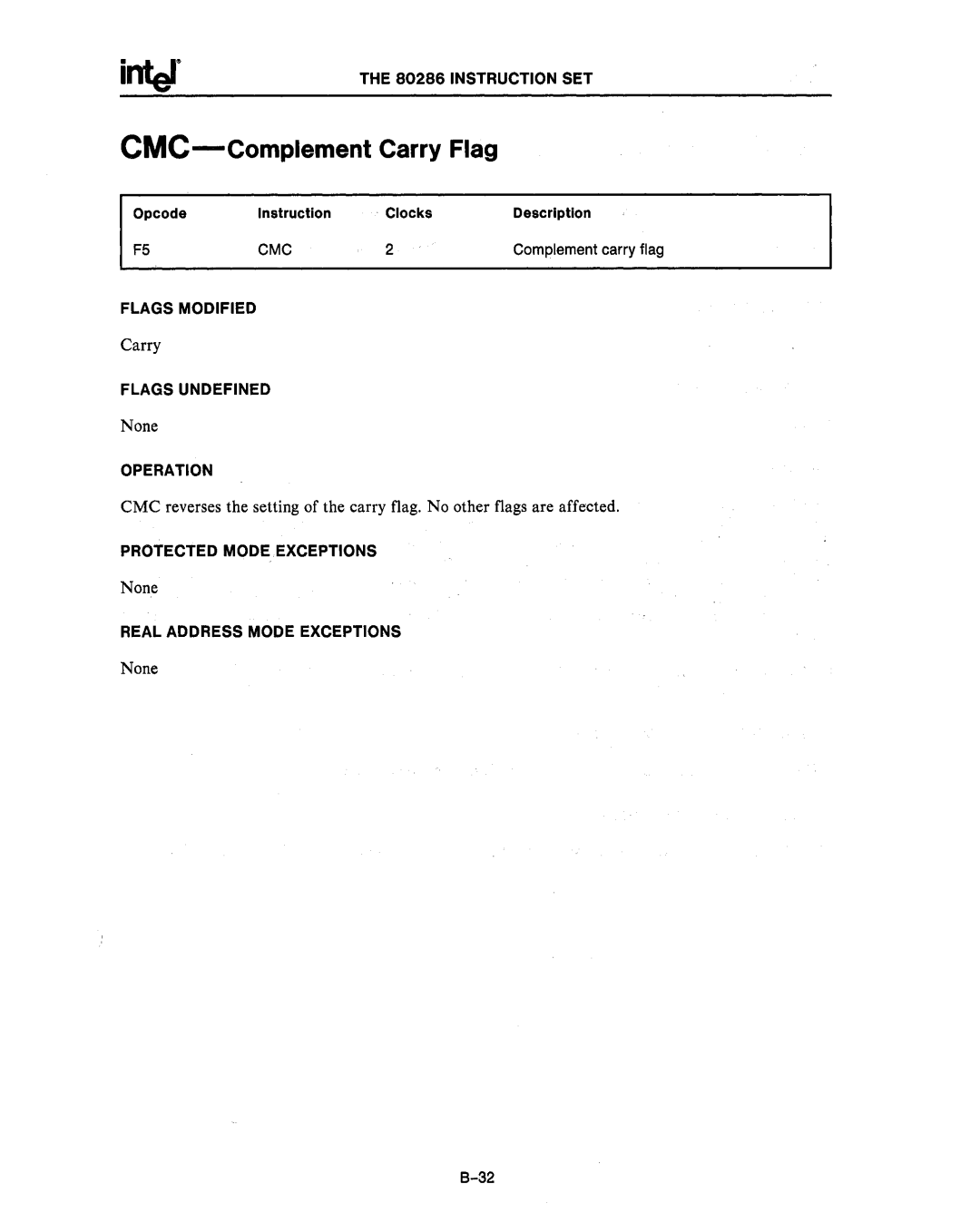

OpcodeInstruction . ClocksDescription

F5 | CMC | 2 | Complement carry flag |

FLAGS MODIFIED

Carry

FLAGS UNDEFINED

None

OPERATION

CMC reverses the setting of the carry flag. No other flags are affected.

PROTECTED MODE. EXCEPTIONS

None

REAL ADDRESS MODE EXCEPTIONS

None