PROGRAMMING NUMERIC APPLICATIONS

|

|

|

|

|

| INCREASING ADDRESSES |

|

|

|

| ||

|

| 15 | CONTROL WORD | ~ 15 |

| CONTROL WORD | ||||||

|

|

|

| STATUS WORD |

|

|

|

|

| STATUS WORD | ||

|

|

|

| TAG WORD |

| +4 |

|

|

|

| TAG WORD | |

|

| INSTRUCTION POINTER |

|

|

|

|

| IP OFFSET | ||||

INSTRUCTION { |

| INSTRUCTION;)1' I | INSTRUCTION |

|

|

|

|

|

| |||

POINTER |

|

|

|

| CS SELECTOR | |||||||

|

| POINTER | OPCODE |

|

|

|

|

|

| |||

OPERAND { |

|

| DATA POINTER |

| ·10 |

|

|

| DATA OPERAND OFFSET | |||

POINTER |

| DATA POINTER I |

|

|

|

|

|

|

|

| ||

|

| 0 |

| .12 |

|

| DATA OPERAND SELECTOR | |||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| SIGNIFICAND | +14 |

|

|

|

| SIGNIFICAND | |||

|

|

| SIGNIFICAND 31·16 | +1. |

|

|

|

| 51GNIFICAND 31·16 | |||

TOPSTA |

|

| SIGNIFICAND 47·32 | +\8 |

| TOP STA |

|

| SIGNIFICANO 47·32 | |||

ELEMENT;ST |

|

|

| |||||||||

|

|

|

|

| ELEMENT :ST |

|

|

| ||||

| '"{ | SIGNIFICAND 63·48 | +20 |

|

| '"{ | SIGNIFICAND 63·48 | |||||

|

| s\ |

| EXPONENT 14·0 | +22 |

|

|

| 5\ |

| EXPONENT | |

|

|

| SIGNIFICAND 15·0 | +2' |

|

|

|

| SIGNIFICAND | |||

|

| L |

|

| +2. |

|

|

| L |

| ||

|

|

| SIGNIFICANO 31·16 |

|

|

|

| SIGNIFICAND 31·16 | ||||

NEXTSTAC K |

| 51GNIFICAND 47·32 | +28 |

| NEXT STAC K |

| SIGNIFICAND 47·32 | |||||

ELEMENT:ST(1 ) |

|

| ElEMENT:ST(I) |

| ||||||||

|

|

| SIGNIFICAND 63·48 | +30 |

|

|

|

| SIGNIFICAND 63·48 | |||

|

|

|

| EXPONENT 14·0 | +32 |

|

|

|

|

| EXPONENT | |

|

|

| SIGNIFICAND 15·0 | +84 |

|

|

|

| SIGNIFICAND | |||

|

|

| SIGNIFICAND | +8. |

|

|

|

| SlGNIF1CAND 31·16 | |||

LAST STAC |

| SIGNIFfCAND 47·32 | +88 |

| LAST STA |

| SIGNIFICAND 47·32 | |||||

ELEMENT:ST~{ |

| ELEMENT:ST(7)'"{ | ||||||||||

SIGNIFICAND 63·48 | +90 |

| SIGNIFICAND 63·48 | |||||||||

|

| Sl |

| EXpm~Em | +92 |

|

|

| 5\ |

| EXPONENT | |

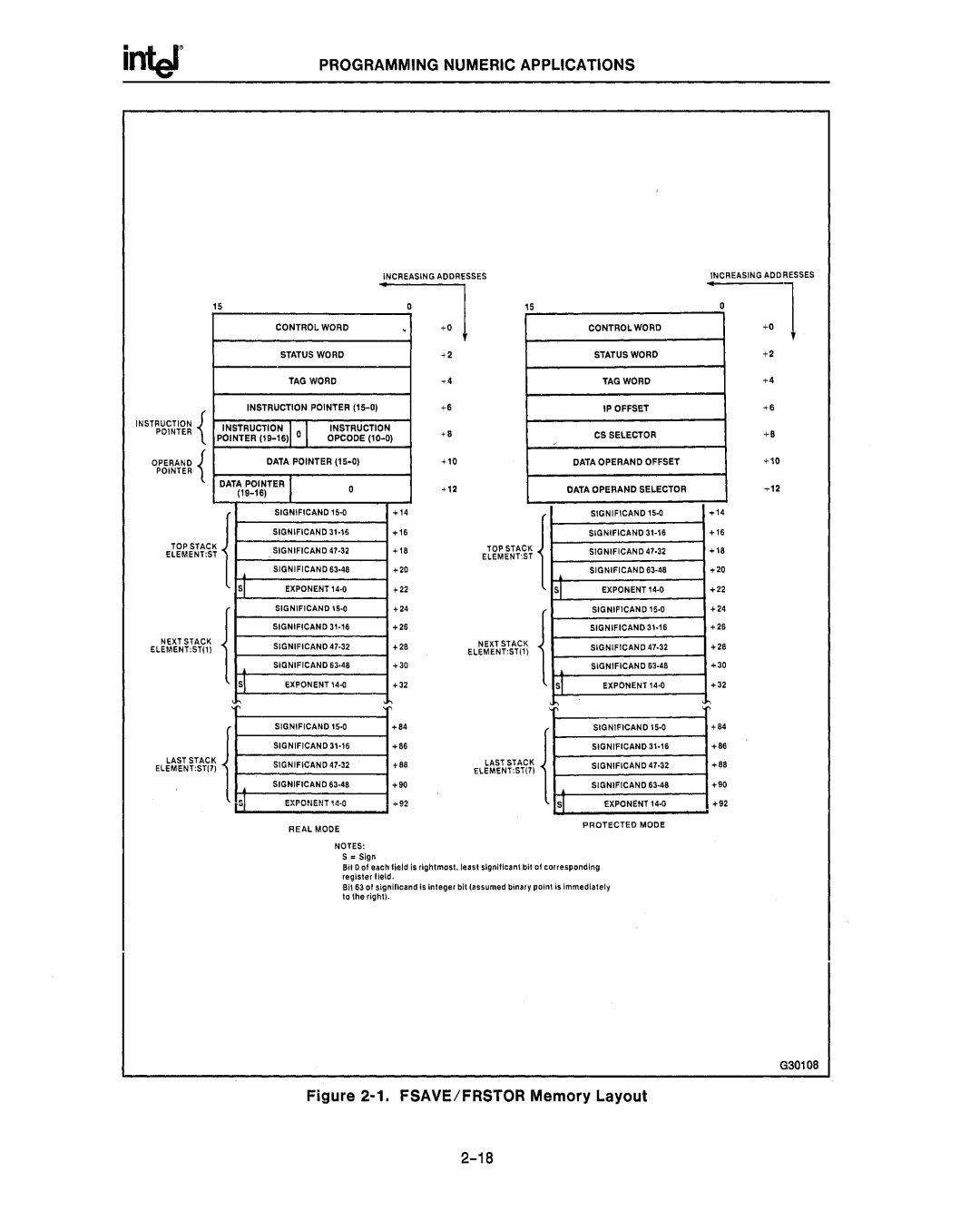

REAL MODE | PROTECTED MODE |

| |

NOTES: |

|

S= Sign

Bit 0 01 each field is rightmost. least slgnilicant bit of corresponding register field.

Bit 63 of signiflcand is integer bit (assumed binary point is Immediately to the righl).

Figure 2-1. FSAVE/FRSTOR Memory Layout

.INCREASING ADDRESSES1

+4

+6

+8

+10

+12

+14

+1.

+18

+20

+22

+"

+2.

+28

+30

+32

+8'

+8.

+88

+90

+92

G30108