intel" | ADVANCED TOPICS |

ASSEJIIBLER INVOKED BV:

LOC DBJ

liB

DotD

DODD ID

DOD' IE

0002 II···. ODDS 81D8 0007 DF 00C8 DDDA 2HC DDOC DFOI oDOE .FA

DO DF 3ID8 0000 00'3 7~ 12

ASM286,86 :FS:5WHPl.AB6

LI HE | SOURCE |

' . 1 "lllaC'Swltch the NPl Cont!!!t on Ftrst Use Af.ter "Task Switch') 2

3 |

| 5'111 teh_npx_conhxt |

~ |

| nltch_"PCcontut |

5 | publiC | |

6 | utrn | lut_npl_task :word |

7

8Thl! Interrupt hlndler '11111 !wltch thl! NPI cantu! If I new tuk

915 attU'lpt1ng to US! the NPl contelt of IInother task lifter 'a '"k

'0 |

| switch. | If the NPl context belong' \0 the current tuk. nothing hlppens. | |||||||||||

"'2 |

| A trap ga\! should be placed In IDT entry 7 rehrrIng to thl! routine. | ||||||||||||

13 |

| The | DPt | of | thl! Slltl! | sholl.)d | be 0 to prevent spoofing. | The"code uglll!nt | ||||||

,~ |

| mu 5t | be | at | pr Iv IItge | !eve 1 | O. |

|

|

|

|

|

| |

'5 |

| The kernel ~tl.Ct 15 u'!UlIIed to overley the TSS Ind the'HPI uv'e area | ||||||||||||

'6 |

| |||||||||||||

| II p laced | at the end | of the | TSS | artl. |

|

|

|

| |||||

'7 |

|

|

|

|

| |||||||||

18 |

| II globll word vlfllble LAST_HPX_TASK Ident1Hu the TSS ulectar of | ||||||||||||

'9 |

| |||||||||||||

20 |

| thl lilt tilt to UII! thl HPX. |

|

|

| I Off II! t .f HPX live Irel ., TSS | ||||||||

f, | ., |

|

|

|

|

|

|

|

|

|

| |||

22 | npl_IIVI_lrt!:1 |

| eq,u |

| urd ,ptr |

| ~ ~ |

| ||||||

23 | IIjut |

|

| IIgmen t |

|

|

|

|

|

|

|

| ||

2~ |

| tlrnll _ udl |

|

| " | publIC |

|

|

|

|

| |||

25 |

| IW 1 t ch_n p I_C 0 n t IX t |

|

| weCO) |

|

|

|

|

| ||||

28 |

| proc |

| far |

|

|

|

|

| |||||

27 |

|

|

| .. |

|

|

|

| I Savi worHng rlgllhr . | |||||

18 |

|

|

|

|

|

|

| |||||||

29 |

| '",ov |

| dl |

|

|

|

| I | 'Get, Iddrul | of Id of lI~t HPI 'lit | |||

3D |

|

| IXtllg 11I'_npx_tllt | |||||||||||

3' |

|

| dl, IX |

|

|

|

| Ge t | Id | of t hI! til t |

| |||

32 |

| ". |

|

|

|

|

|

|

|

| ||||

33 |

|

|

|

|

|

|

|

| Rell'lGve | APL | Held |

| ||

| "d |

|

|

|

|

|

|

|

|

| tilt |

|

| |

3~ |

| c 1t I |

|

|

|

|

|

|

| Cll1r | ulhhed | fllg | ||

36 |

| ,I • |

|

|

|

|

|

|

| No | interrupti 1II0wedi | |||

38 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

| omp |

| IX, dllll' t_npl_ill t |

| I | Sit | 1 f |

|

|

| |||

39 |

|

|

| 111111 | \ II k |

| ||||||||

~ , |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

~ 0 |

| I' |

| uml_ tllt |

|

|

|

|

|

|

|

|

| |

DO IS 87050000 00'9 050800 DD'C 8ED8 ODIE DD362C 00 0022 36DD26BOO 0027

0027 If

0028 58

0029 CF

II.WARNING '160. LINE

<2 | xchg | IX , d I l III t_ npx_ t II k |

H | odd | 11,8 |

~ .~ | ,ov | dl,11 |

45.hne dl:npl_Ilve_lru

~6f r ~ \0 r "lnpI_!IVI_lrll

47 | llIme_iul: |

|

~ 8 | p.p | d. |

~ 9 | p.p |

|

SO | lret |

|

5' |

| udp |

52 |

| |

53 |

|

|

S4 | kerneLcode | ends |

154, SEGIHHT CDHTAIHS PRIVILEGED INSTRUCTIOHS

55ud

Set new tuk ld ud glt old Go to TSS 11111

"Address TSS of previoul HPI tllk Sive old NPI S\I\I

I Get current NPX state

I Retllrn to Interrupted program

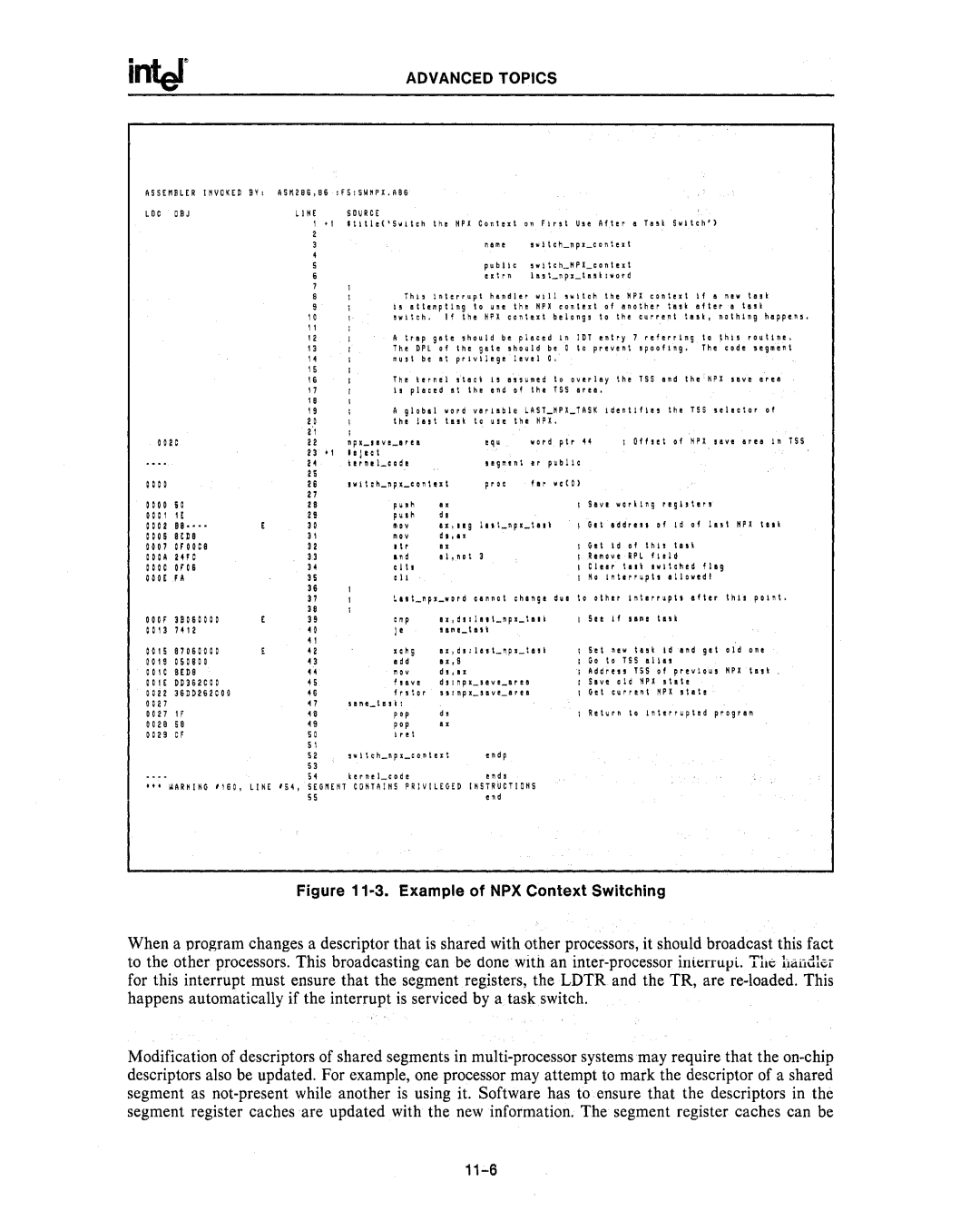

Figure 11-3. Example of NPX Context Switching

When a program changes a descriptor that is shared with other processors, it should broadcast this fact to the other processors. This broadcasting can be done with .an

Modification of descriptors of shared segments in