infer

INTERRUPTS AND EXCEPTIONS

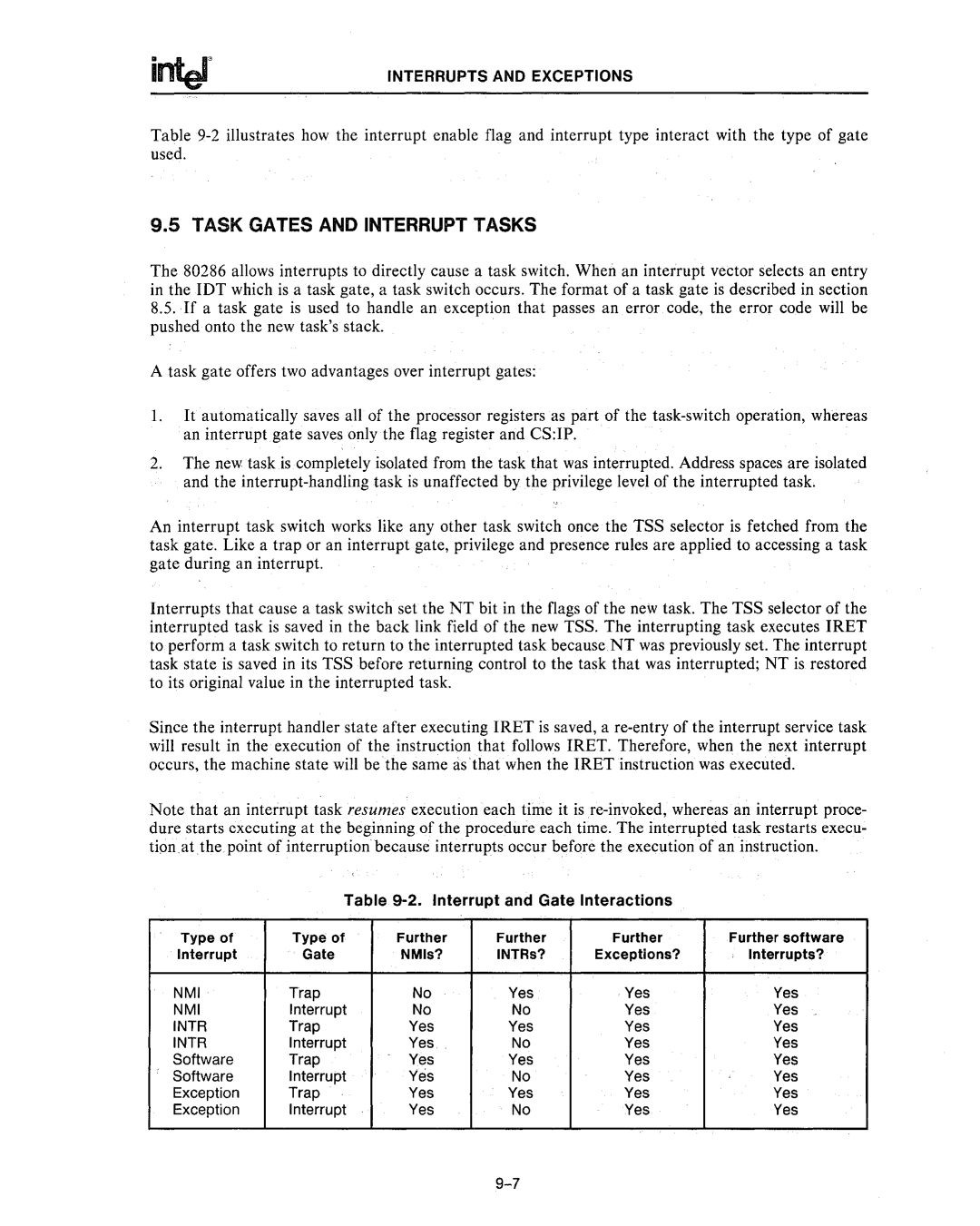

Table

9.5 TASK GATES AND INTERRUPT TASKS

The 80286 allows interrupts to directly cause a task switch. When an interrupt vector selects an entry in the IDT which is a task gate, a task switch occurs. The format of a task gate is described in section

8.5.If a task gate is used to handle an exception that passes an error code, the error code will be pushed onto the new task's stack.

A task gate offers two advantages over interrupt gates:

1.It automatically saves all of the processor registers as part of the

2.The new task is completely isolated from the task that was interrupted. Address spaces are isolated and the

An interrupt task switch works like any other task switch once the TSS selector is fetched from the task gate. Like a trap or an interrupt gate, privilege and presence rules are applied to accessing a task gate during an interrupt.

Interrupts that cause a task switch set the NT bit in the flags of the new task. The TSS selector of the interrupted task is saved in the back link field of the new TSS. The interrupting task executes IRET to perform a task switch to return to the interrupted task because.NT was previously set. The interrupt task state is saved in its TSS before returning control .to the task that was interrupted; NT is restored to its original value in the interrupted task.

Since the interrupt handler state after executing IRET is saved, a

Note that an interrupt task resumes execution each time it is

Table 9-2. Interrupt and Gate Interactions

Type of | Type of | Further | Further | Further | Further software |

Interrupt | Gate | NMls? | INTRs? | Exceptions? | Interrupts? |

NMI | Trap | No | Yes | Yes | Yes |

NMI | Interrupt | No | No | Yes | Yes |

INTR | Trap | Yes | Yes | Yes | Yes |

INTR | Interrupt | Yes | No | Yes | Yes |

Software | Trap | Yes | Yes | Yes | Yes |

Software | Interrupt | Yes | No | Yes | Yes |

Exception | Trap | Yes | Yes | Yes | Yes |

Exception | Interrupt | Yes | No | Yes | Yes |